Temat zakładam głównie w celu motywacji mnie do działania, ponieważ ostatnio mam mało czasu na hobby, a chciałbym zrobić sobie coś unikalnego :)

Co to za projekt? O co chodzi? Nazwa tematu na pewno jest ciekawa, ponieważ niektórzy wiedzą, że jestem przeciwnikiem standardowych NOS DAC'ów, ale to nie znaczy, że odrzucam ten pomysł całkowicie. Generalnie zaczęło się od pomysłu interpolacji liniowej w prostym filtrze cyfrowym na FPGA, którego stworzyłem przy okazji układu nad którym w wolnym czasie pracuję z kolegą taz (odbiornik SPDIF/I2S, re-clocker, wybór formatu wyjściowego oraz długości słowa, itd.). Na forum zapytałem kolegę raven1985 co myśli o takiej interpolacji i wspomniał, że ciekawe może być zrobienie tego analogowo:

http://diyaudio.pl/showthread.php/25...169#post471169

Oczywiście zaciekawiło mnie to i znalazłem temat o którym wspomniał raven1985:

http://www.diyaudio.com/forums/digit...-tda1541a.html

O co tutaj chodzi? Pisząc krótko, jest to interpolacja liniowa po stronie analogowej gdzie każdy z DAC'ów z wyjściem prądowym dostaje takie same dane, które są opóźnione czasowo. Prąd na wyjściu przetworników jest sumowany i zamiast jednego skoku (z jednego DAC'a), mamy utworzoną drabinkę z powodu czasowo opóźnionego sumowania prądów z kilku DAC'ów. Teoretycznie działa to tylko z DAC'ami, które posiadają prądowe wyjścia, ale nic nie szkodzi na przeszkodzie "pokombinowania" z DAC'ami z wyjściem napięciowym, ale raczej nie ma to sensu i byłoby to znacznie więcej roboty.

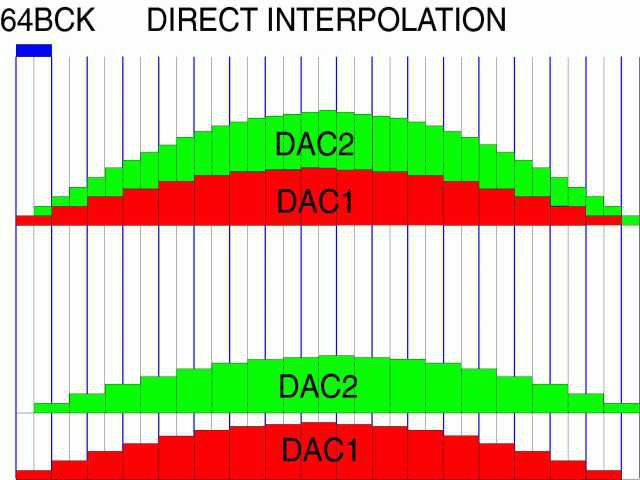

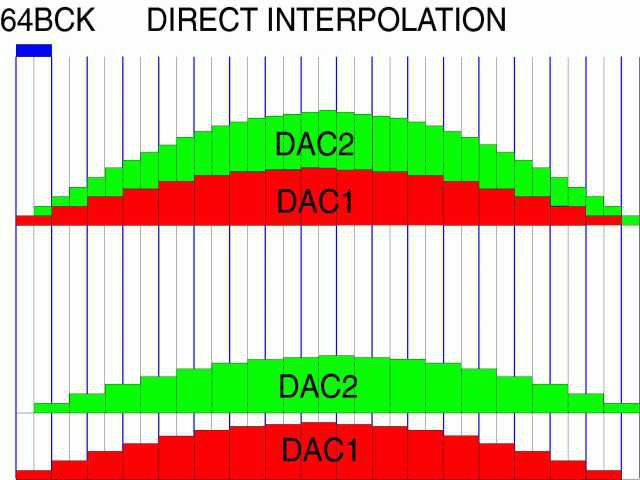

Pewnie większość dalej nie wie o co chodzi, ale nie ma to jak graficzna reprezentacja, którą zapożyczyłem z diyaudio.com:

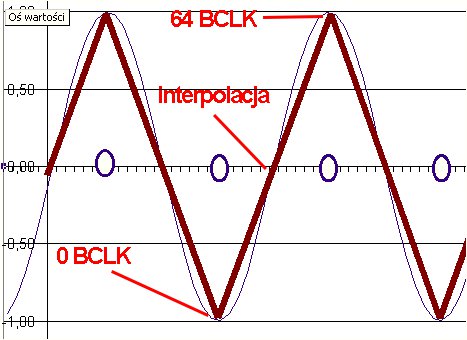

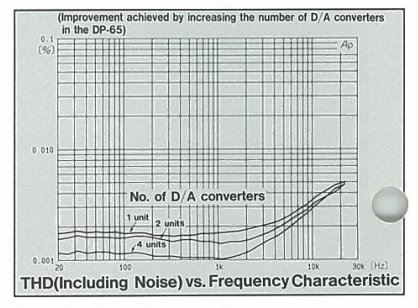

Na zdjęciu są dwa DAC'i z wyjściem prądowym (sumowanym z obu przetworników) i opóźnioną linią danych dla drugiego DAC'a. Teraz wyobraźmy sobie, że 64BCK = 44,1 kHz. O co w tym chodzi? Prąd na wyjściu DAC'a zmienia się zgodnie z częstotliwością próbkowania - w tym wypadku 44,1 kHz. No jest to normalna sprawa, ponieważ co 44,1 kHz otrzymuje nową próbkę PCM do konwersji na wartość analogową. Stworzenie analogowego filtru, który wytnie tą częstotliwość, a zostawi pasmo audio (powiedzmy do 22,05 kHz), jest bardzo trudne, a nawet jak się uda, to pewnie będzie grać jak kupa. No fajnie byłoby jakoś podnieść częstotliwość próbkowania i to właśnie robią filtry cyfrowe, ale nie tylko - generalnie ich zadaniem jest interpolowanie fali audio. Głównym odsłuchowym problemem NOS DAC'ów (pomijam problemy techniczne syfu wysoko częstotliwościowego) są odbicia wracające do pasma audio, które normalnie są przesuwane wyżej dzięki nadpróbkowaniu i zostają wycięte przez filtr dolnoprzepustowy. Odbicia zamiast powstawać przy lustrze na 22,05 kHz, jak to bywa przy próbkowaniu 44,1 kHz bez dodatkowego nadpróbkowania, są przesuwane wyżej, przykładowo przy nadpróbkowaniu 8x otrzymujemy częstotliwość 352,8 kHz i nasze początkowe lustro powstanie dopiero przy 330,75 kHz co już jest łatwo wyciąć przy użyciu prostego filtra 2-rzędu.

Trochę się rozpisałem, a miałem tylko wyjaśnić jak to działa. Dla przypomnienia - pierwszy DAC "wydala" z siebie próbki w formie prądu zgodnie z częstotliwością wejściową, czyli 44,1 kHz. Drugi DAC ma opóźnioną linię danych o równe 32BCK, czyli w połowie trwania próbki z pierwszego DAC'a (np. 1 mA), dodaje swoją wartość, taka samą, czyli na wyjściu mamy już 2 mA. Jak łatwo można zauważyć, zwiększyliśmy częstotliwość próbkowania do 88,2 kHz bez żadnego filtru cyfrowego. Prąd wzrasta liniowo, czyli wirtualna próbka, którą dodaliśmy, znajduje się pomiędzy pierwszą próbką a drugą (tzw. liniowa interpolacja). To wszystko bez użycia filtru cyfrowego. Oczywiście nie ma tak różowo, ponieważ taka interpolacja generalnie ma wiele wad, ale coś za coś. Przykładowo nie jesteśmy w stanie odtworzyć fali sinusoidalnej o częstotliwości 20 kHz. Dlaczego? Ponieważ mamy tylko dwie próbki, a interpolacja liniowa co najwyżej połączy te dwa punkty i będzie zadowolona ze swojego wyniku :) Filtr cyfrowy z prawdziwego zdarzenia odtworzy prawdziwą sinusoidę mając tylko dwie próbki! No, ale nie słuchamy sinusów, więc może warto spróbować?

Wszystko fajnie, ale dlaczego DAC bez filtru cyfrowego? Dla dobrego grania? Być może, ale jest jedna techniczna rzecz, która w tym wypadku nie jest subiektywna - odpowiedź impulsowa.

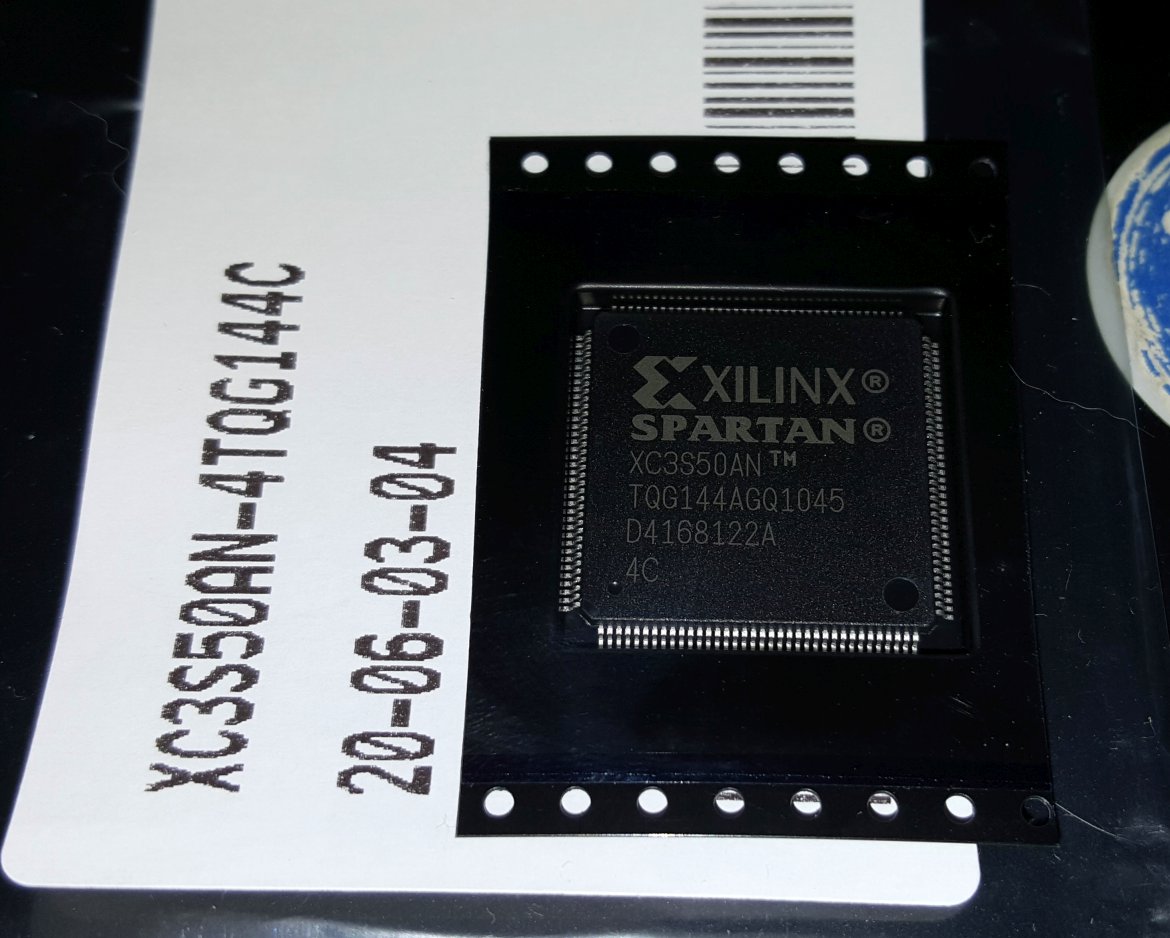

W każdym wypadku gościu z tematu na diyaudio.com nawalił dużą ilość rejestrów przesuwnych i różnych zabawek, aby ten cel osiągnąć. Niestety lub stety ja nie mam zamiaru się tak bawić i całą logiką zajmie się układ FPGA od Xilinx'a, a dokładniej Spartan-3 XC3S50AN. Dlaczego wersja AN? A no znowu - z lenistwa, ten typ rodziny Spartan-3 ma wbudowaną pamięć Flash typu non-volatile. Nie ma potrzeby dodawania zewnętrznego PROM'u do załadowania konfiguracji FPGA. Cały opis sprzętu będzie zrobiony w VHDL'u, ponieważ niestety nie jestem fanem Veriloga :) Dlaczego FPGA a nie CPLD? Więcej miejsca, więcej możliwości, więcej pinów i... tyle wystarczy :)

Założenia projektu:

- Wirtualne próbkowanie na poziomie 705,6 kHz przy wejściowym próbkowaniu 44,1 kHz. Inaczej mówiąc 16-krotne wirtualne "nadpróbkowanie". Wymaga to aż 16 DAC'ów na kanał.

- DAC - AD1865N-K w ilości 16 sztuk (stereo), ponieważ taki mogłem otrzymać w większej ilości i dobrej cenie. Na początku chciałem użyć TDA1541A, ale cena nawet zwykłej wersji 1541A jest tak zaporowa, że odechciewa się wszystkiego. Oczywiście do takiego DAC'a chciałem tylko i wyłącznie kostkę typu multi-bit (np. R-2R jakim jest AD1865N).

- Linia zegarowa DAC (CLK) wspólna dla wszystkich DAC'ów z każdego kanału.

- Linie danych DAC (DL i DR) wspólne dla wszystkich DAC'ów z każdego kanału.

- Linie zatrzasku danych (LL i LR) osobne dla każdego DAC'a. Będą użyte do cyfrowego opóźnienia zatrzaśnięcia danych (po wyłączeniu CLK). W datasheet nie ma jasnej informacji, czy są one synchroniczne czy asynchroniczne względem CLK, ale jest informacja, że zatrzaśnięcie danych następuje podczas zbocza opadającego na LL i LR, co sugeruje, że są asynchroniczne.

- 4-warstwowe PCB z powodu trudności w prawidłowym prowadzeniu masy.

- Płytka logiczne podzielona na analog - cyfra - analog (kanał lewy - częśc cyfrowa razem z FPGA - kanał prawy). AD1865N jest tak fajnie zrobiony, że część cyfrowa jest u "dołu" i można to logicznie rozdzielić. Prądy powrotne nie będą błądziły po masie przy płytce typu mixed-signal ze wspólną wylewką masy.

- Osobne zasilanie dla kanału lewego i prawego (konektory ułożone zgodnie z logicznym rozstawieniem).

- Osobne zasilanie części cyfrowej (konektor ułożony zgodnie z logicznym rozstawieniem).

- Warstwa górna i dolna - cyfrowe sygnały i logicznie na części analogowej - sumowanie prądów od wszystkich kości.

- Warstwa pierwsza środkowa - zasilanie.

- Warstwa druga środkowa - wylewka masy.

- Wyjście prądowe - układ I/V na innej płytce.

- Każdy DAC ma własny regulator 7805, 7905 oraz drugi 7805 dla części cyfrowej. Cudów nie trzeba - referencyjne napięcia dla drabinki tworzone są wewnątrz DAC'a przez układy typu bandgap.

- Cyfrowe wejścia danych w DAC'ach będą sterowane prosto z FPGA (LVTTL / LVCMOS33 - nib DAC pracuje przy TTL, ale wg. datasheet stan wysoki jest już rozpoznawany od 2,0V).

- Wejście tylko i wyłącznie I2S.

- FPGA nie będzie pracował we własnej domenie zegarowej, chociaż tak na początku myślałem. Cały DAC będzie wymagał linii MCLK od I2S.

- DAC bez problemu łyknie grube formaty jak np. 24 / 192 kHz. Przy ucięciu BCLK do 32x Fs (czyli generalnie 16-bitów), można ciągnąć i 384 kHz.

Chyba na razie tyle :P Zgodnie z regulaminem, muszę dodać jakieś zdjęcie. No to poniżej przedstawiam kostki AD1865N-K (starsze wykonanie z mojej ulubionej fabryki w Filipinach, rocznik 92 z oznaczeniami grawerowanymi laserowo):

Ciąg dalszy nastąpi.

Co to za projekt? O co chodzi? Nazwa tematu na pewno jest ciekawa, ponieważ niektórzy wiedzą, że jestem przeciwnikiem standardowych NOS DAC'ów, ale to nie znaczy, że odrzucam ten pomysł całkowicie. Generalnie zaczęło się od pomysłu interpolacji liniowej w prostym filtrze cyfrowym na FPGA, którego stworzyłem przy okazji układu nad którym w wolnym czasie pracuję z kolegą taz (odbiornik SPDIF/I2S, re-clocker, wybór formatu wyjściowego oraz długości słowa, itd.). Na forum zapytałem kolegę raven1985 co myśli o takiej interpolacji i wspomniał, że ciekawe może być zrobienie tego analogowo:

http://diyaudio.pl/showthread.php/25...169#post471169

Oczywiście zaciekawiło mnie to i znalazłem temat o którym wspomniał raven1985:

http://www.diyaudio.com/forums/digit...-tda1541a.html

O co tutaj chodzi? Pisząc krótko, jest to interpolacja liniowa po stronie analogowej gdzie każdy z DAC'ów z wyjściem prądowym dostaje takie same dane, które są opóźnione czasowo. Prąd na wyjściu przetworników jest sumowany i zamiast jednego skoku (z jednego DAC'a), mamy utworzoną drabinkę z powodu czasowo opóźnionego sumowania prądów z kilku DAC'ów. Teoretycznie działa to tylko z DAC'ami, które posiadają prądowe wyjścia, ale nic nie szkodzi na przeszkodzie "pokombinowania" z DAC'ami z wyjściem napięciowym, ale raczej nie ma to sensu i byłoby to znacznie więcej roboty.

Pewnie większość dalej nie wie o co chodzi, ale nie ma to jak graficzna reprezentacja, którą zapożyczyłem z diyaudio.com:

Na zdjęciu są dwa DAC'i z wyjściem prądowym (sumowanym z obu przetworników) i opóźnioną linią danych dla drugiego DAC'a. Teraz wyobraźmy sobie, że 64BCK = 44,1 kHz. O co w tym chodzi? Prąd na wyjściu DAC'a zmienia się zgodnie z częstotliwością próbkowania - w tym wypadku 44,1 kHz. No jest to normalna sprawa, ponieważ co 44,1 kHz otrzymuje nową próbkę PCM do konwersji na wartość analogową. Stworzenie analogowego filtru, który wytnie tą częstotliwość, a zostawi pasmo audio (powiedzmy do 22,05 kHz), jest bardzo trudne, a nawet jak się uda, to pewnie będzie grać jak kupa. No fajnie byłoby jakoś podnieść częstotliwość próbkowania i to właśnie robią filtry cyfrowe, ale nie tylko - generalnie ich zadaniem jest interpolowanie fali audio. Głównym odsłuchowym problemem NOS DAC'ów (pomijam problemy techniczne syfu wysoko częstotliwościowego) są odbicia wracające do pasma audio, które normalnie są przesuwane wyżej dzięki nadpróbkowaniu i zostają wycięte przez filtr dolnoprzepustowy. Odbicia zamiast powstawać przy lustrze na 22,05 kHz, jak to bywa przy próbkowaniu 44,1 kHz bez dodatkowego nadpróbkowania, są przesuwane wyżej, przykładowo przy nadpróbkowaniu 8x otrzymujemy częstotliwość 352,8 kHz i nasze początkowe lustro powstanie dopiero przy 330,75 kHz co już jest łatwo wyciąć przy użyciu prostego filtra 2-rzędu.

Trochę się rozpisałem, a miałem tylko wyjaśnić jak to działa. Dla przypomnienia - pierwszy DAC "wydala" z siebie próbki w formie prądu zgodnie z częstotliwością wejściową, czyli 44,1 kHz. Drugi DAC ma opóźnioną linię danych o równe 32BCK, czyli w połowie trwania próbki z pierwszego DAC'a (np. 1 mA), dodaje swoją wartość, taka samą, czyli na wyjściu mamy już 2 mA. Jak łatwo można zauważyć, zwiększyliśmy częstotliwość próbkowania do 88,2 kHz bez żadnego filtru cyfrowego. Prąd wzrasta liniowo, czyli wirtualna próbka, którą dodaliśmy, znajduje się pomiędzy pierwszą próbką a drugą (tzw. liniowa interpolacja). To wszystko bez użycia filtru cyfrowego. Oczywiście nie ma tak różowo, ponieważ taka interpolacja generalnie ma wiele wad, ale coś za coś. Przykładowo nie jesteśmy w stanie odtworzyć fali sinusoidalnej o częstotliwości 20 kHz. Dlaczego? Ponieważ mamy tylko dwie próbki, a interpolacja liniowa co najwyżej połączy te dwa punkty i będzie zadowolona ze swojego wyniku :) Filtr cyfrowy z prawdziwego zdarzenia odtworzy prawdziwą sinusoidę mając tylko dwie próbki! No, ale nie słuchamy sinusów, więc może warto spróbować?

Wszystko fajnie, ale dlaczego DAC bez filtru cyfrowego? Dla dobrego grania? Być może, ale jest jedna techniczna rzecz, która w tym wypadku nie jest subiektywna - odpowiedź impulsowa.

W każdym wypadku gościu z tematu na diyaudio.com nawalił dużą ilość rejestrów przesuwnych i różnych zabawek, aby ten cel osiągnąć. Niestety lub stety ja nie mam zamiaru się tak bawić i całą logiką zajmie się układ FPGA od Xilinx'a, a dokładniej Spartan-3 XC3S50AN. Dlaczego wersja AN? A no znowu - z lenistwa, ten typ rodziny Spartan-3 ma wbudowaną pamięć Flash typu non-volatile. Nie ma potrzeby dodawania zewnętrznego PROM'u do załadowania konfiguracji FPGA. Cały opis sprzętu będzie zrobiony w VHDL'u, ponieważ niestety nie jestem fanem Veriloga :) Dlaczego FPGA a nie CPLD? Więcej miejsca, więcej możliwości, więcej pinów i... tyle wystarczy :)

Założenia projektu:

- Wirtualne próbkowanie na poziomie 705,6 kHz przy wejściowym próbkowaniu 44,1 kHz. Inaczej mówiąc 16-krotne wirtualne "nadpróbkowanie". Wymaga to aż 16 DAC'ów na kanał.

- DAC - AD1865N-K w ilości 16 sztuk (stereo), ponieważ taki mogłem otrzymać w większej ilości i dobrej cenie. Na początku chciałem użyć TDA1541A, ale cena nawet zwykłej wersji 1541A jest tak zaporowa, że odechciewa się wszystkiego. Oczywiście do takiego DAC'a chciałem tylko i wyłącznie kostkę typu multi-bit (np. R-2R jakim jest AD1865N).

- Linia zegarowa DAC (CLK) wspólna dla wszystkich DAC'ów z każdego kanału.

- Linie danych DAC (DL i DR) wspólne dla wszystkich DAC'ów z każdego kanału.

- Linie zatrzasku danych (LL i LR) osobne dla każdego DAC'a. Będą użyte do cyfrowego opóźnienia zatrzaśnięcia danych (po wyłączeniu CLK). W datasheet nie ma jasnej informacji, czy są one synchroniczne czy asynchroniczne względem CLK, ale jest informacja, że zatrzaśnięcie danych następuje podczas zbocza opadającego na LL i LR, co sugeruje, że są asynchroniczne.

- 4-warstwowe PCB z powodu trudności w prawidłowym prowadzeniu masy.

- Płytka logiczne podzielona na analog - cyfra - analog (kanał lewy - częśc cyfrowa razem z FPGA - kanał prawy). AD1865N jest tak fajnie zrobiony, że część cyfrowa jest u "dołu" i można to logicznie rozdzielić. Prądy powrotne nie będą błądziły po masie przy płytce typu mixed-signal ze wspólną wylewką masy.

- Osobne zasilanie dla kanału lewego i prawego (konektory ułożone zgodnie z logicznym rozstawieniem).

- Osobne zasilanie części cyfrowej (konektor ułożony zgodnie z logicznym rozstawieniem).

- Warstwa górna i dolna - cyfrowe sygnały i logicznie na części analogowej - sumowanie prądów od wszystkich kości.

- Warstwa pierwsza środkowa - zasilanie.

- Warstwa druga środkowa - wylewka masy.

- Wyjście prądowe - układ I/V na innej płytce.

- Każdy DAC ma własny regulator 7805, 7905 oraz drugi 7805 dla części cyfrowej. Cudów nie trzeba - referencyjne napięcia dla drabinki tworzone są wewnątrz DAC'a przez układy typu bandgap.

- Cyfrowe wejścia danych w DAC'ach będą sterowane prosto z FPGA (LVTTL / LVCMOS33 - nib DAC pracuje przy TTL, ale wg. datasheet stan wysoki jest już rozpoznawany od 2,0V).

- Wejście tylko i wyłącznie I2S.

- FPGA nie będzie pracował we własnej domenie zegarowej, chociaż tak na początku myślałem. Cały DAC będzie wymagał linii MCLK od I2S.

- DAC bez problemu łyknie grube formaty jak np. 24 / 192 kHz. Przy ucięciu BCLK do 32x Fs (czyli generalnie 16-bitów), można ciągnąć i 384 kHz.

Chyba na razie tyle :P Zgodnie z regulaminem, muszę dodać jakieś zdjęcie. No to poniżej przedstawiam kostki AD1865N-K (starsze wykonanie z mojej ulubionej fabryki w Filipinach, rocznik 92 z oznaczeniami grawerowanymi laserowo):

Ciąg dalszy nastąpi.

) w moim przypadku 32bitowy co odpowiada 32 dac-om :)

) w moim przypadku 32bitowy co odpowiada 32 dac-om :)

Skomentuj