Brzmi ciekawie. Czy ostatecznie planujesz udostêpniæ taki filtr dla forumowego zamówienia?

Ciekaw jestem efektów :)

Ciekaw jestem efektów :)

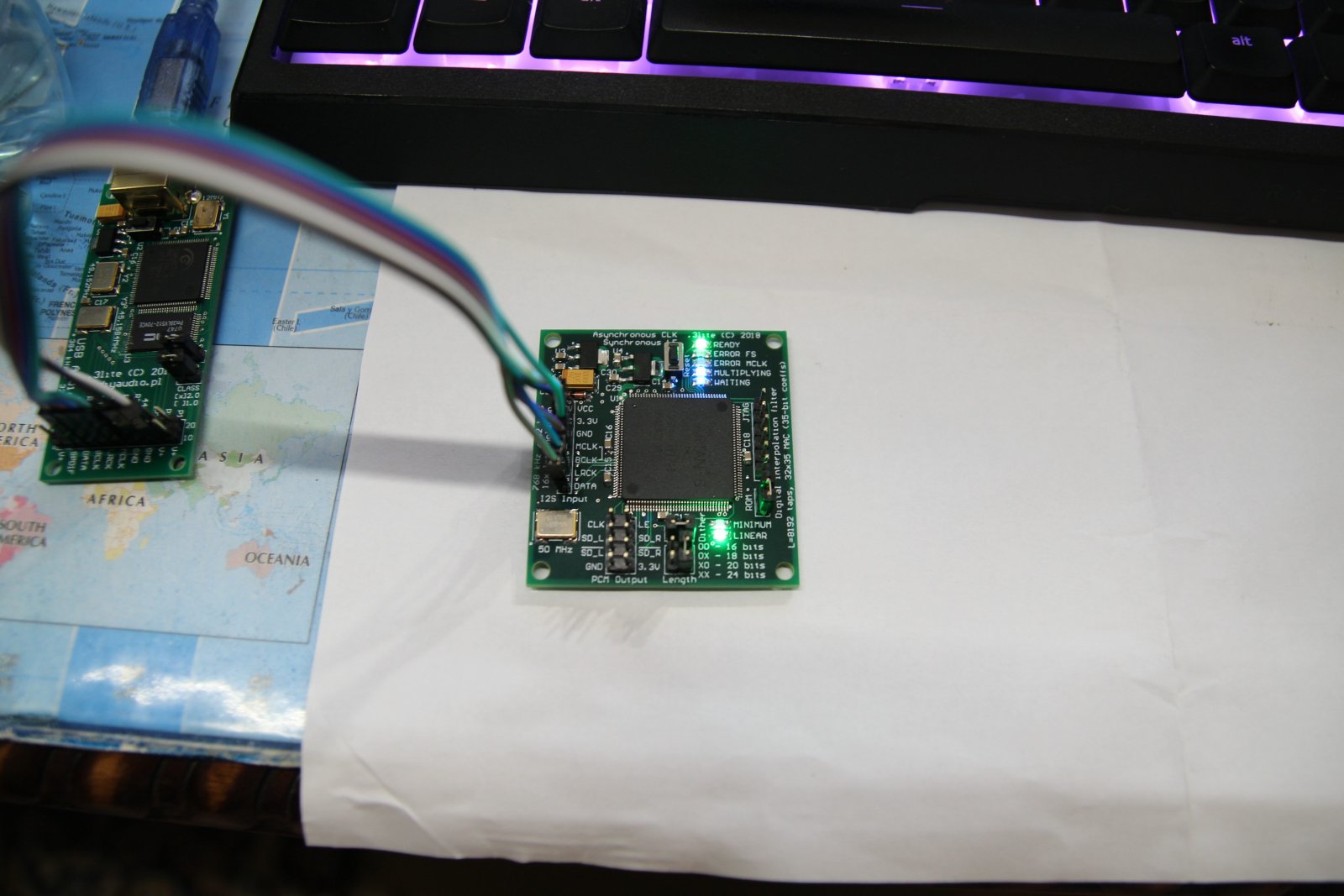

Ten projekt nie bêdzie udostêpniony w stylu USB Audio czy DAC'a na AD1865, ale jak kto¶ bêdzie chcia³ to mo¿e ode mnie wzi±æ gotowy uk³ad do pod³±czenia. Na razie i tak czekam na PCB z fabryki, wiêc jak przyjdzie to bêdê testowa³ finaln± wersjê

Ten projekt nie bêdzie udostêpniony w stylu USB Audio czy DAC'a na AD1865, ale jak kto¶ bêdzie chcia³ to mo¿e ode mnie wzi±æ gotowy uk³ad do pod³±czenia. Na razie i tak czekam na PCB z fabryki, wiêc jak przyjdzie to bêdê testowa³ finaln± wersjê

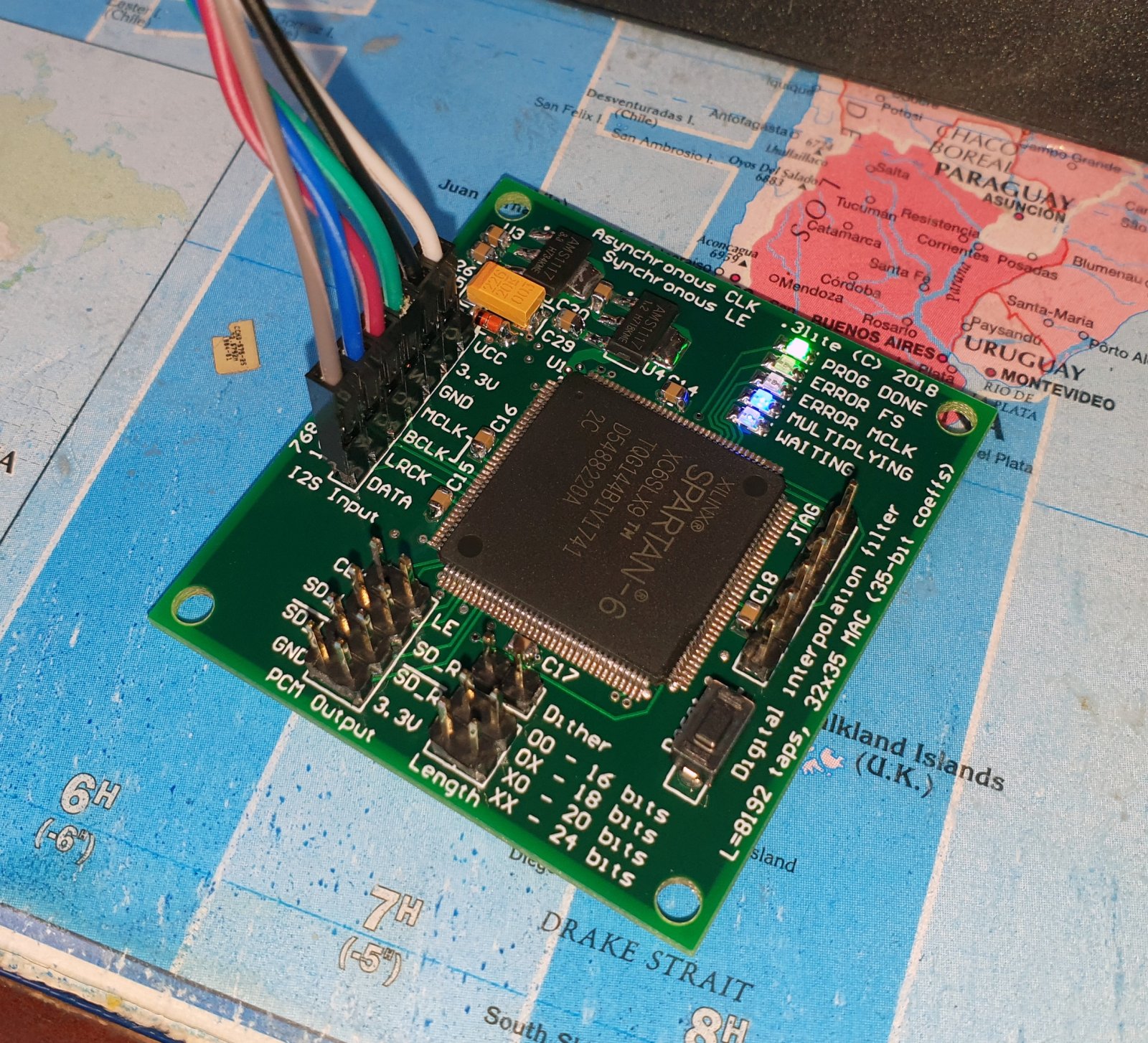

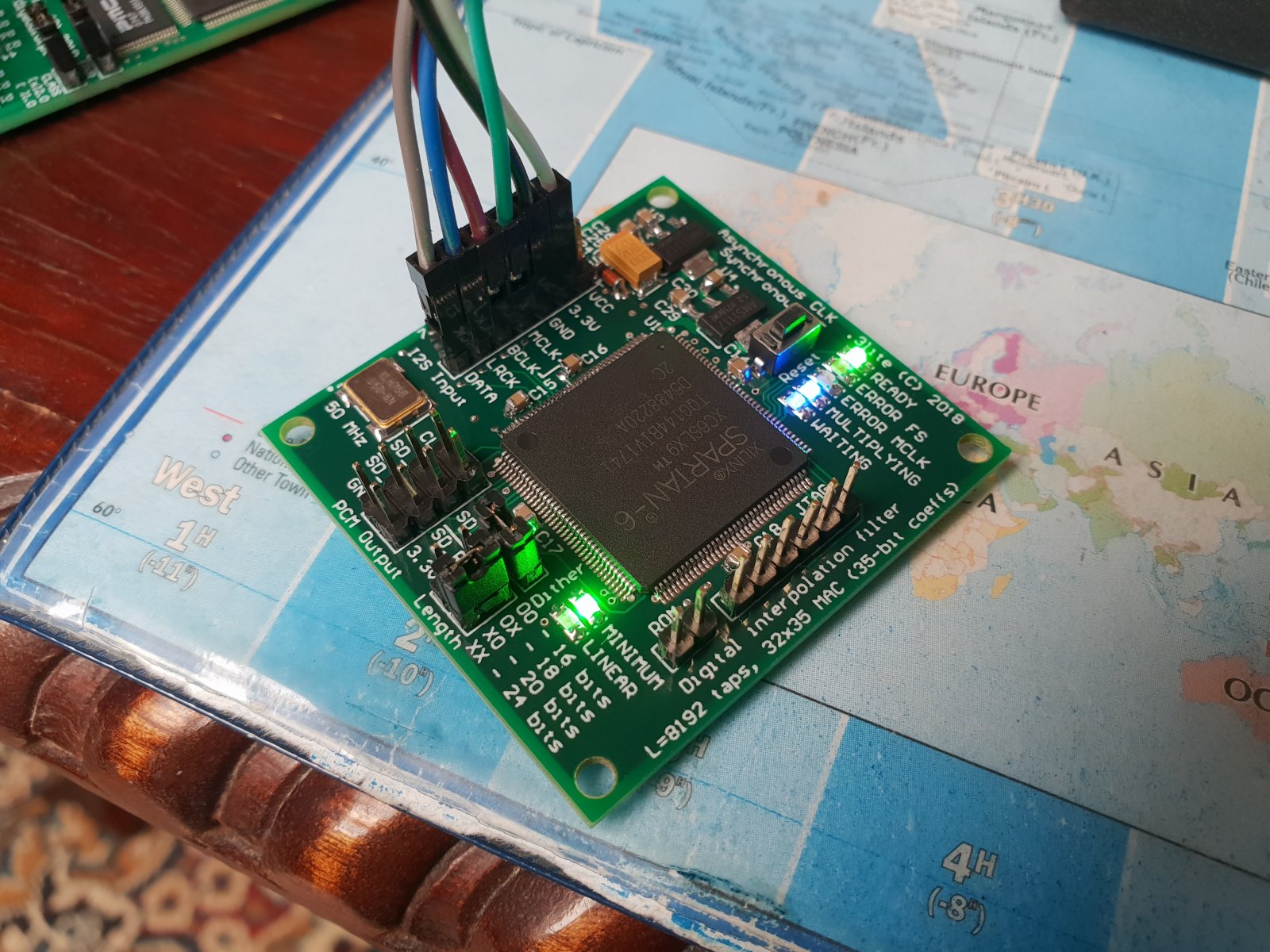

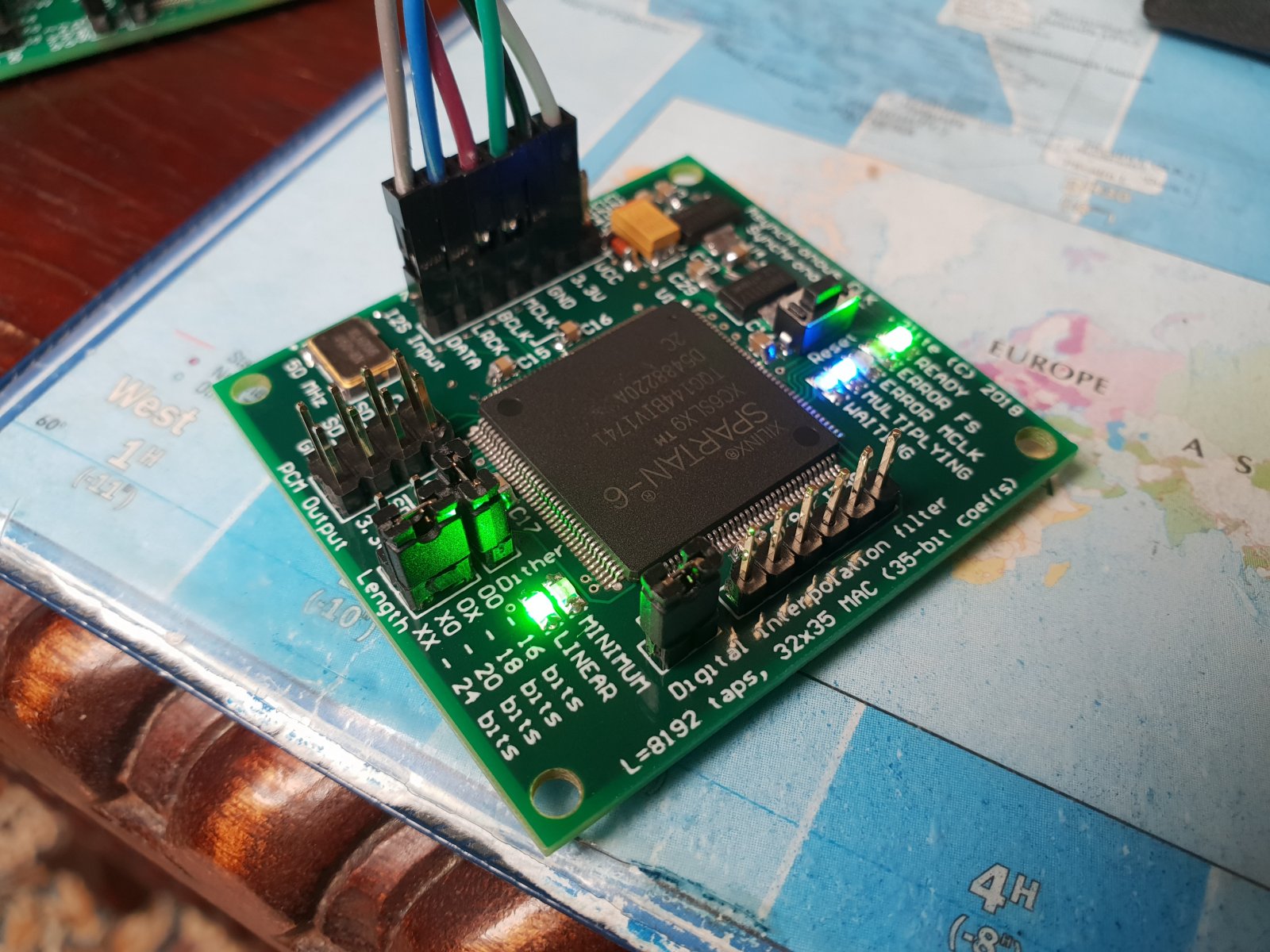

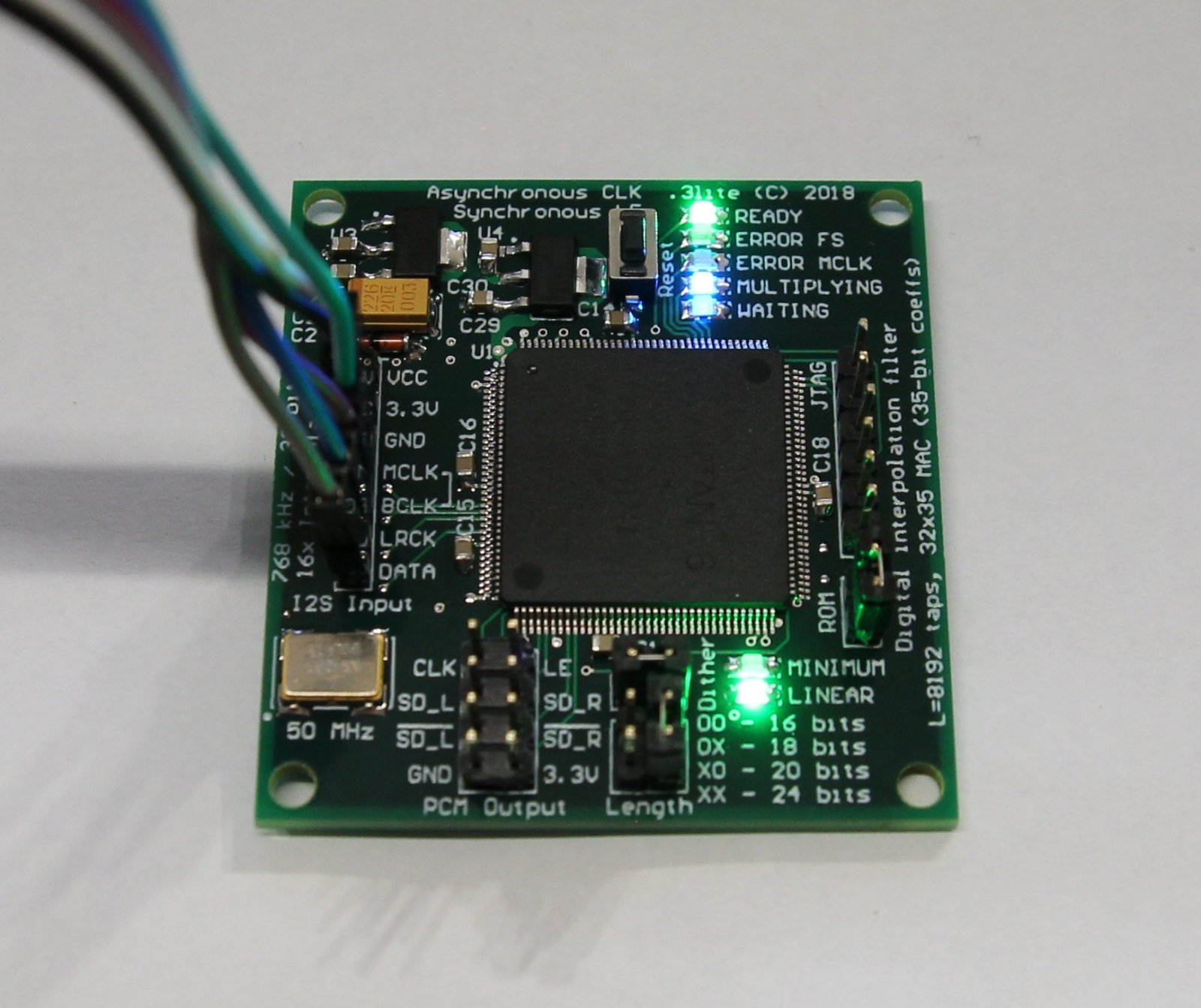

Kilka diodek i tylko takich, które s± faktycznie wymagane i wskazuj± status dzia³ania filtru. Diody "MULTIPLYING" oraz "WAITING" wskazuj± po prostu na to co w danej chwili robi rdzeñ, tj. czy w danej chwili mno¿y i mieli now± próbkê czy po prostu czeka na nastêpn±. Dioda "ERROR FS" wskazuje na b³±d czêstotliwo¶ci wej¶ciowej, która generalnie musi mie¶ciæ siê w zakresie od 44.1 kHz do 768 kHz. Tak samo dioda "ERROR MCLK" wskazuje b³±d od strony zegara MCLK.

Kilka diodek i tylko takich, które s± faktycznie wymagane i wskazuj± status dzia³ania filtru. Diody "MULTIPLYING" oraz "WAITING" wskazuj± po prostu na to co w danej chwili robi rdzeñ, tj. czy w danej chwili mno¿y i mieli now± próbkê czy po prostu czeka na nastêpn±. Dioda "ERROR FS" wskazuje na b³±d czêstotliwo¶ci wej¶ciowej, która generalnie musi mie¶ciæ siê w zakresie od 44.1 kHz do 768 kHz. Tak samo dioda "ERROR MCLK" wskazuje b³±d od strony zegara MCLK.

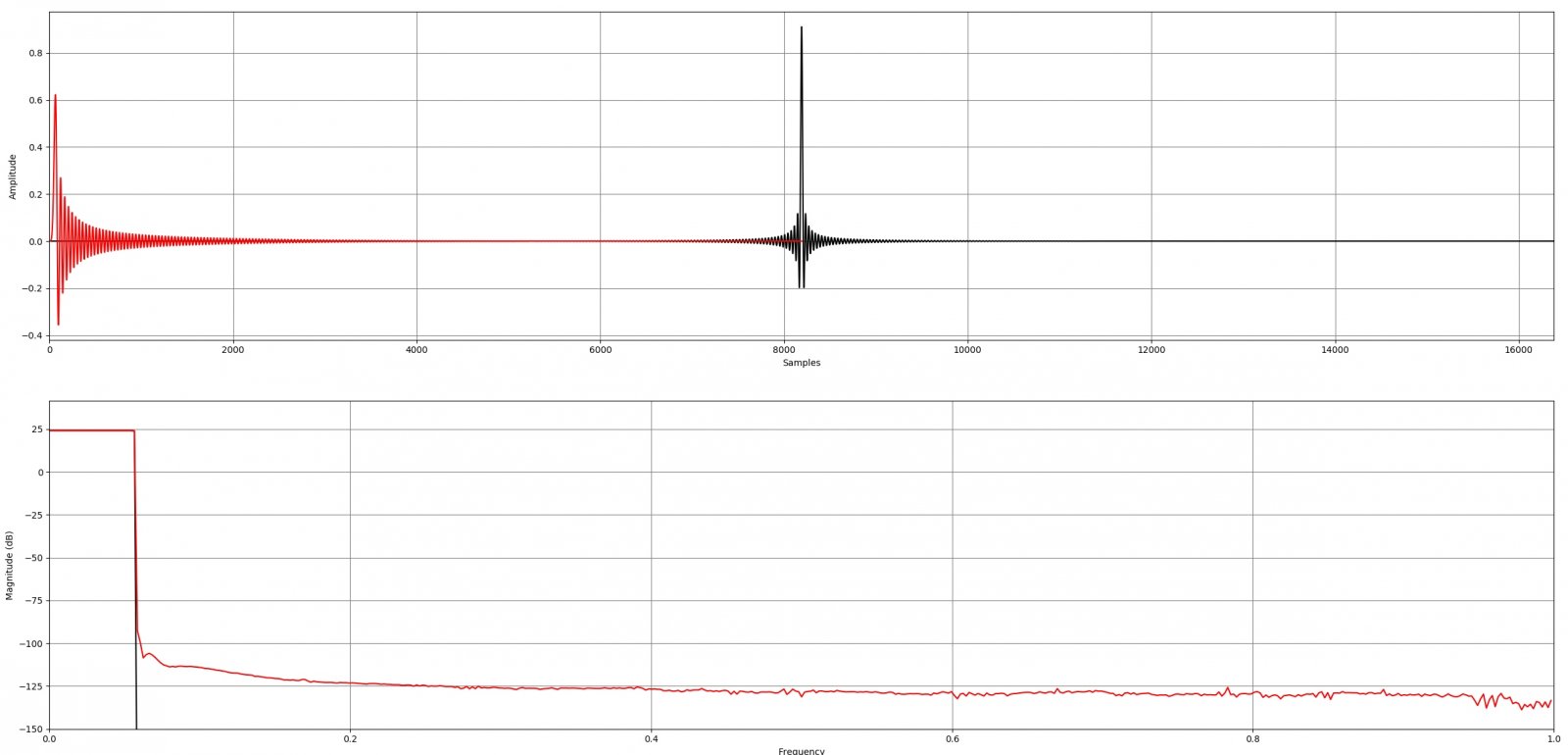

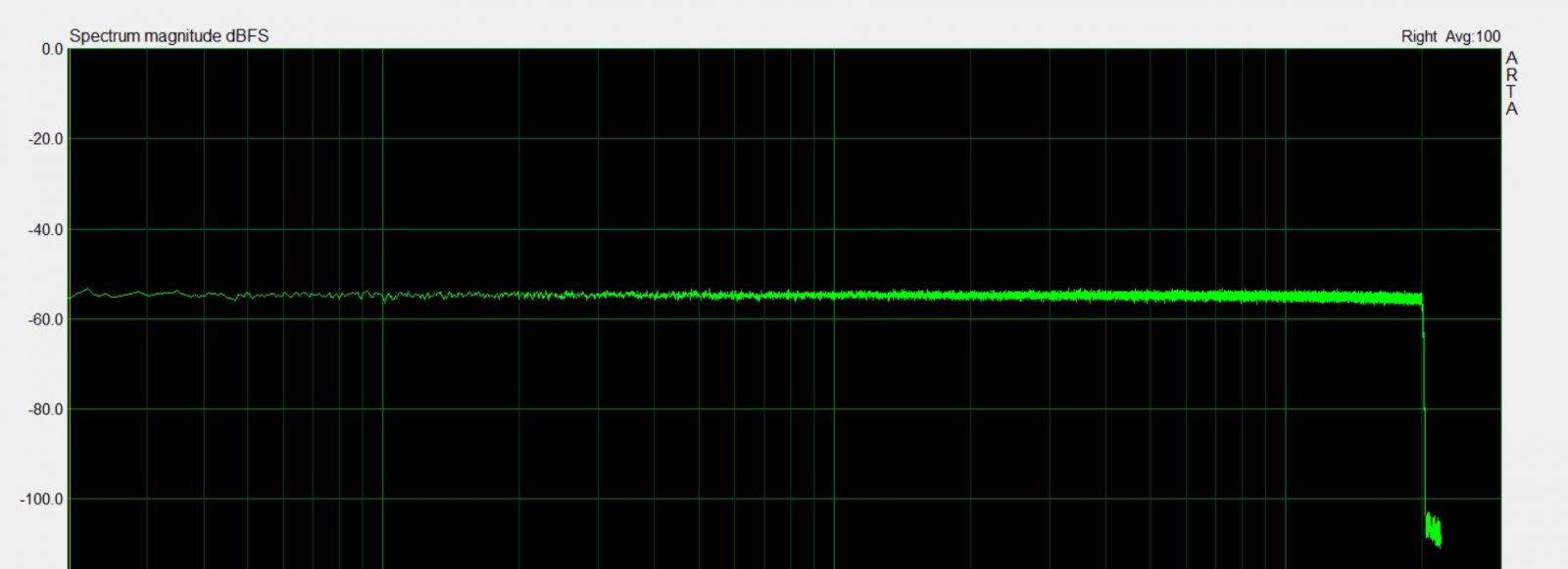

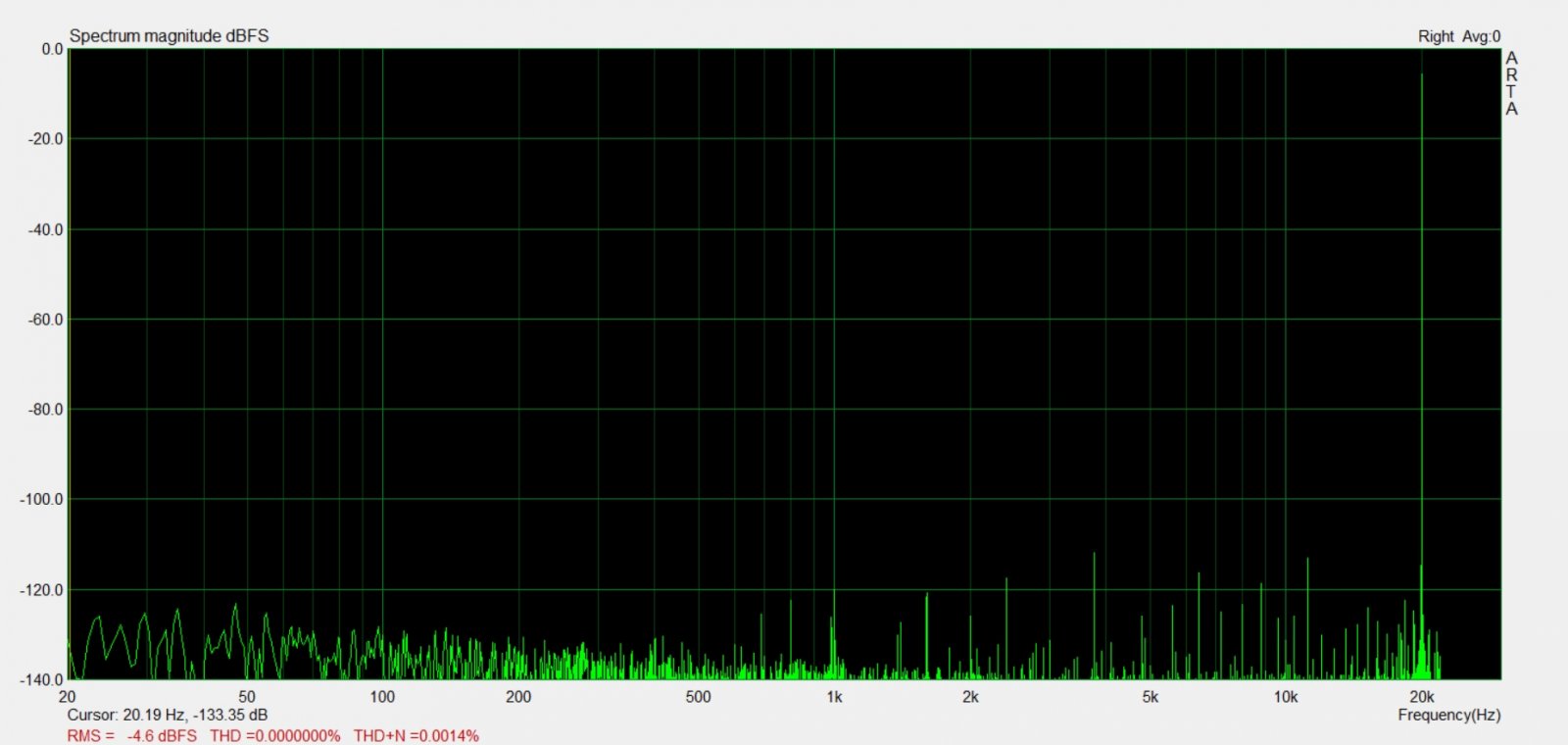

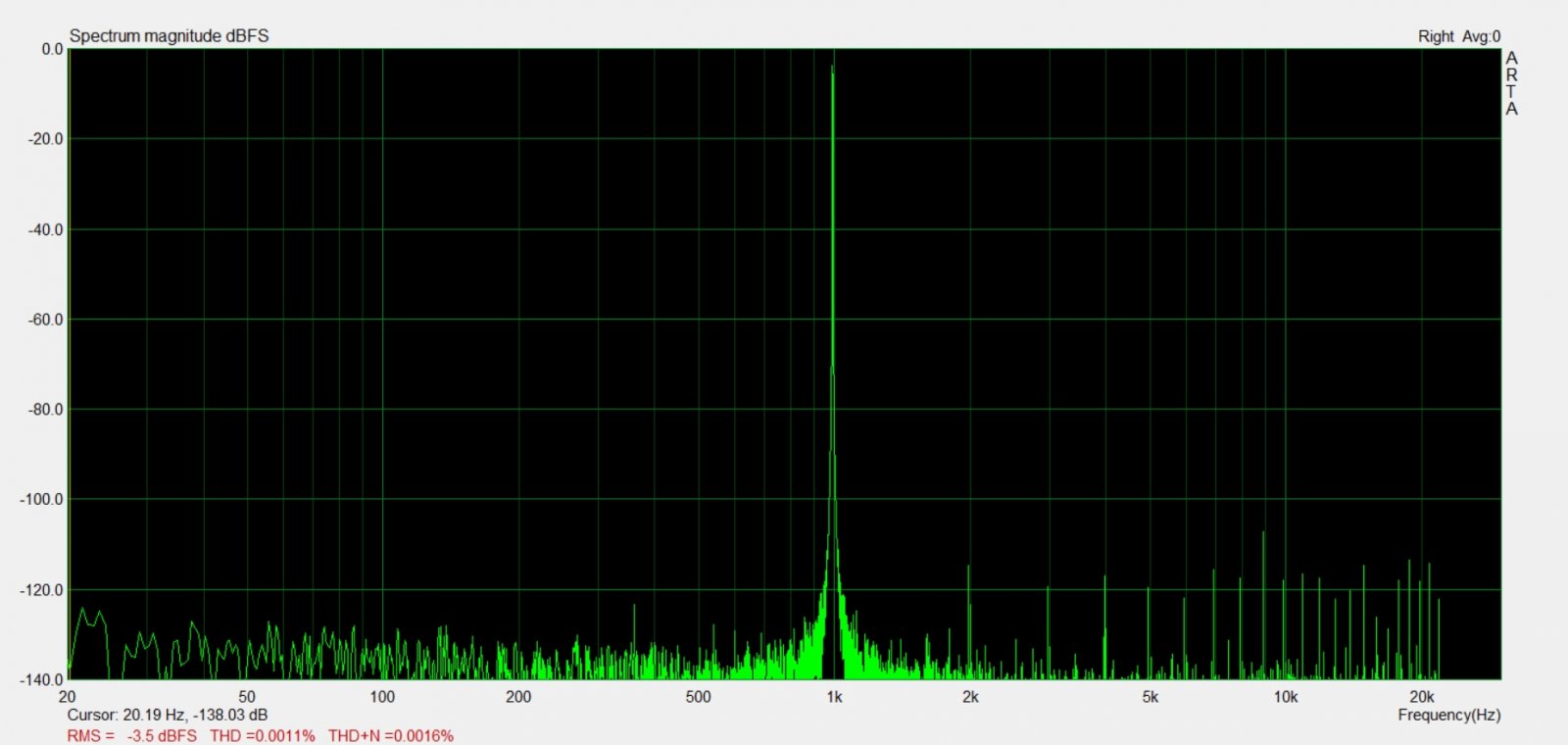

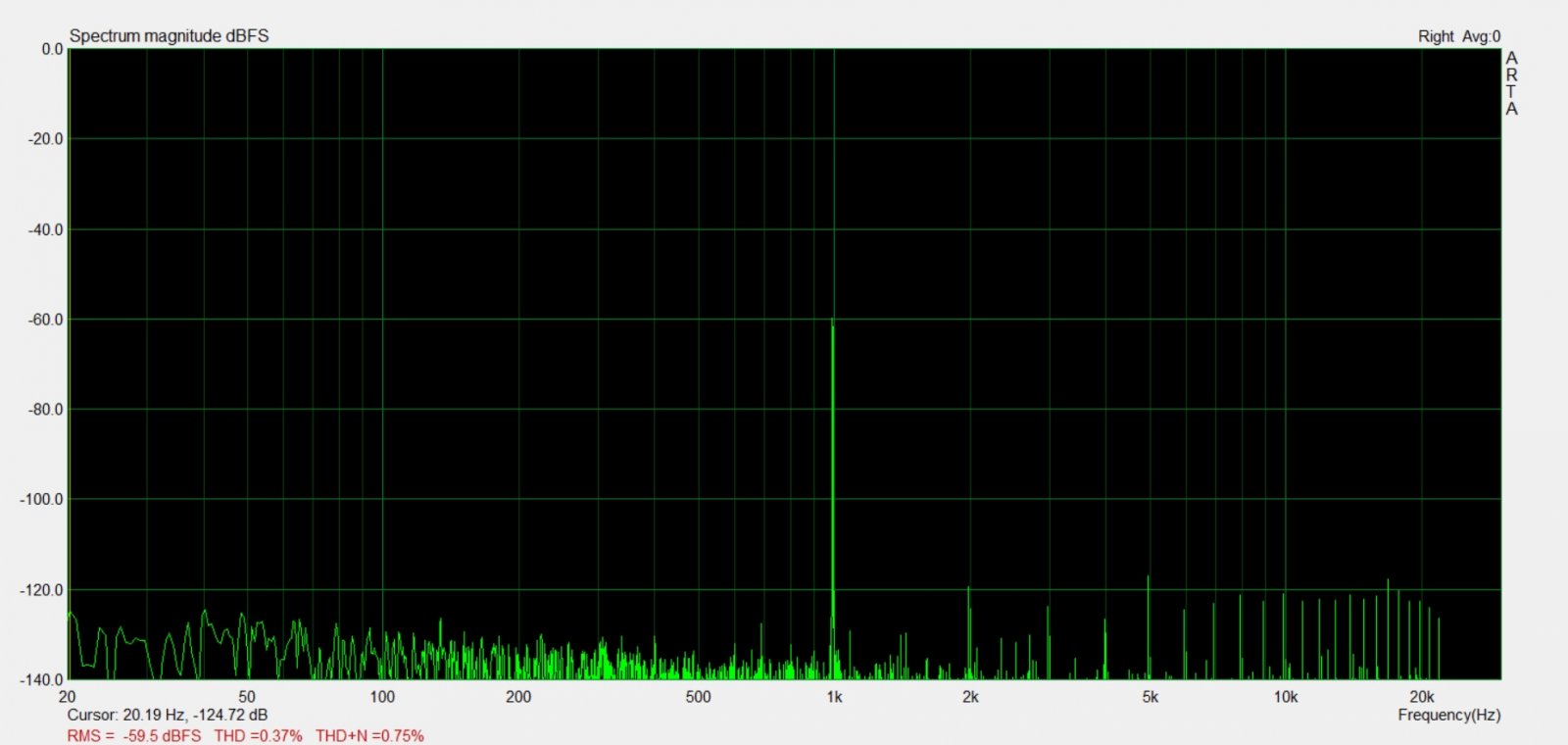

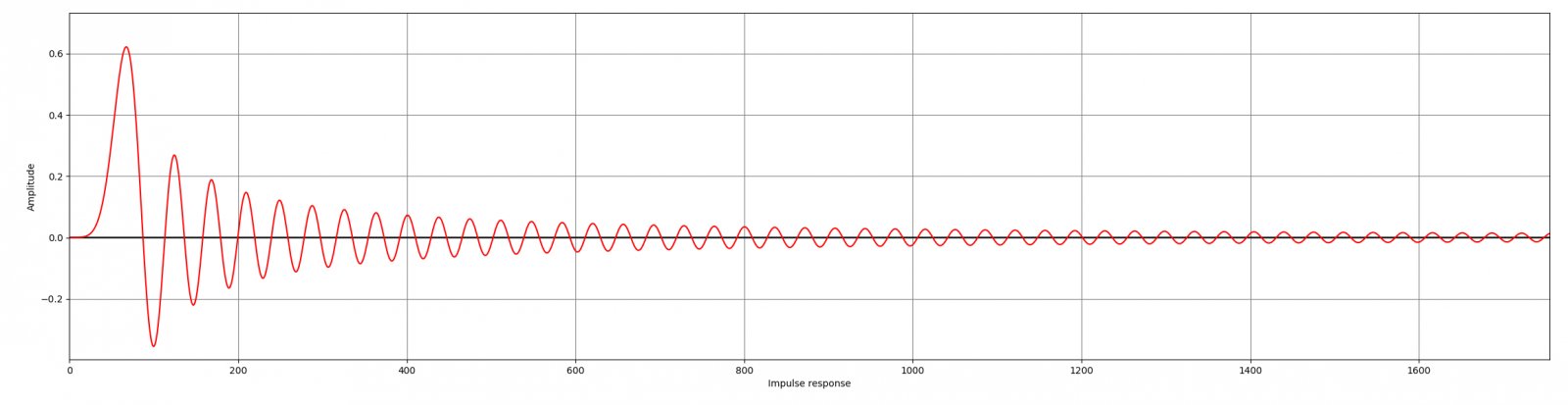

T³umienie obu jest wystarczaj±ce (z czego filtr o liniowej fazie t³umi znacz±co mocniej, ale to s± ró¿nice miêdzy 110 dB a 140+ dB...).

T³umienie obu jest wystarczaj±ce (z czego filtr o liniowej fazie t³umi znacz±co mocniej, ale to s± ró¿nice miêdzy 110 dB a 140+ dB...).

Oczywi¶cie na pewno jakie¶ poprawki bêd±, ale wszystko co by³o mo¿liwe do zrobienia zosta³o zrobione.

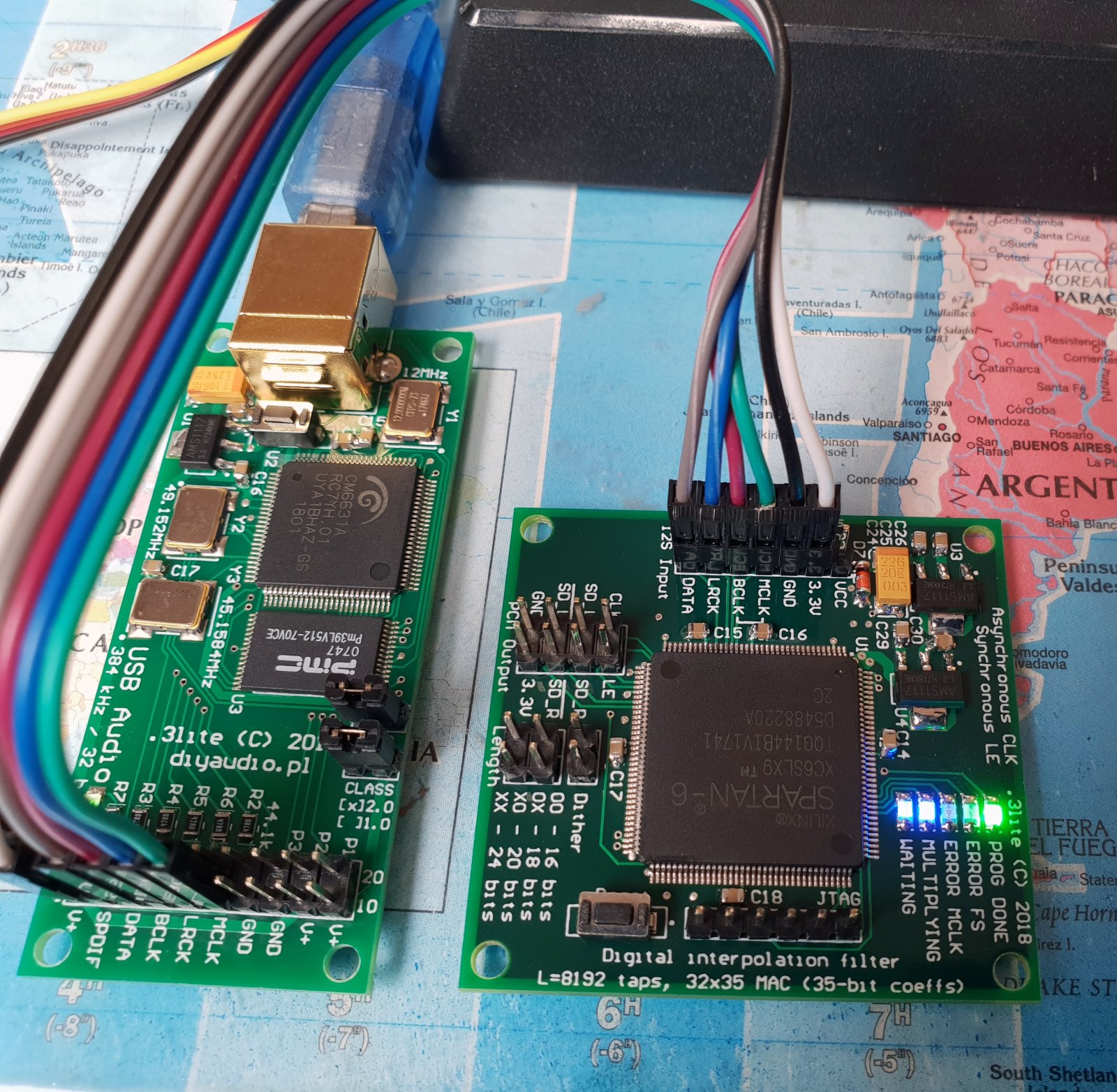

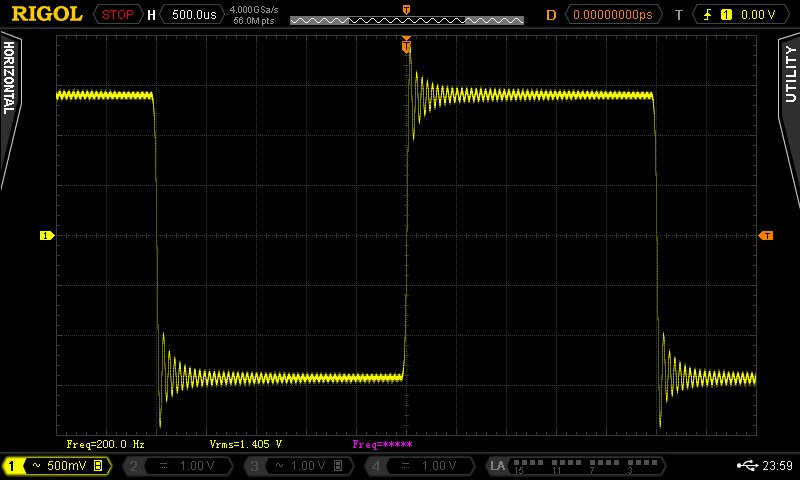

Oczywi¶cie na pewno jakie¶ poprawki bêd±, ale wszystko co by³o mo¿liwe do zrobienia zosta³o zrobione. Dobrze, ¿e nie zamówi³em PCB a stwierdzi³em, ¿e spróbujê to jeszcze dodaæ no i siê uda³o... Ledwo. Na PCB doda³em zworkê "ROM", która podczas w³±czenia zasilania (b±d¼ resetu na micro-switchu) decyduje o tym jakie wspó³czynniki za³adowaæ do pamiêci. Oba filtry s± rzêdu 8192 i po prostu fizycznie nie da siê wiêcej zmie¶ciæ w tym FPGA. Musia³em wej¶ciowe FIFO przerzuciæ do "distributed RAM", poniewa¿ u¿ycia "block RAM" by³o na poziomie 103% a dziêki temu spad³o do 97% i uda³o siê wszystko zmie¶ciæ...

Dobrze, ¿e nie zamówi³em PCB a stwierdzi³em, ¿e spróbujê to jeszcze dodaæ no i siê uda³o... Ledwo. Na PCB doda³em zworkê "ROM", która podczas w³±czenia zasilania (b±d¼ resetu na micro-switchu) decyduje o tym jakie wspó³czynniki za³adowaæ do pamiêci. Oba filtry s± rzêdu 8192 i po prostu fizycznie nie da siê wiêcej zmie¶ciæ w tym FPGA. Musia³em wej¶ciowe FIFO przerzuciæ do "distributed RAM", poniewa¿ u¿ycia "block RAM" by³o na poziomie 103% a dziêki temu spad³o do 97% i uda³o siê wszystko zmie¶ciæ...

Na razie innego DAC'a nie zrobi³em do tego filtru, wiêc jeszcze nie ma na co wymieniæ :)

Na razie innego DAC'a nie zrobi³em do tego filtru, wiêc jeszcze nie ma na co wymieniæ :)

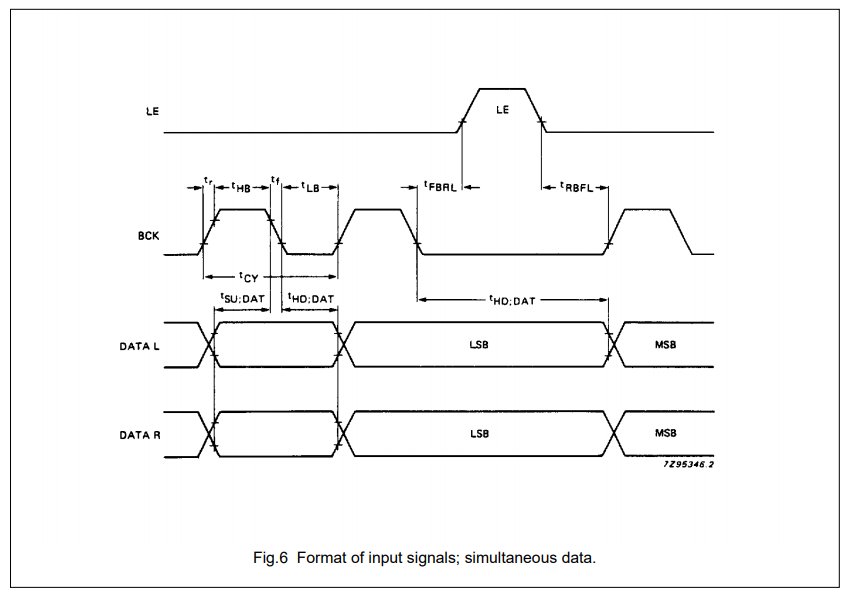

Nie ma mo¿liwo¶ci dodania obs³ugi TDA1541A do g³ównej wersji (16-krotna interpolacja), wiêc finalnie bêd± dwa opisu do tego projektu (16-krotna interpolacja oraz 8-krotna interpolacja z innym formatem wyj¶ciowym dla 16-bitów, wiêc w praktyce ta wersja jest dobra tylko i wy³±cznie dla TDA1541A).

Nie ma mo¿liwo¶ci dodania obs³ugi TDA1541A do g³ównej wersji (16-krotna interpolacja), wiêc finalnie bêd± dwa opisu do tego projektu (16-krotna interpolacja oraz 8-krotna interpolacja z innym formatem wyj¶ciowym dla 16-bitów, wiêc w praktyce ta wersja jest dobra tylko i wy³±cznie dla TDA1541A).

Skomentuj