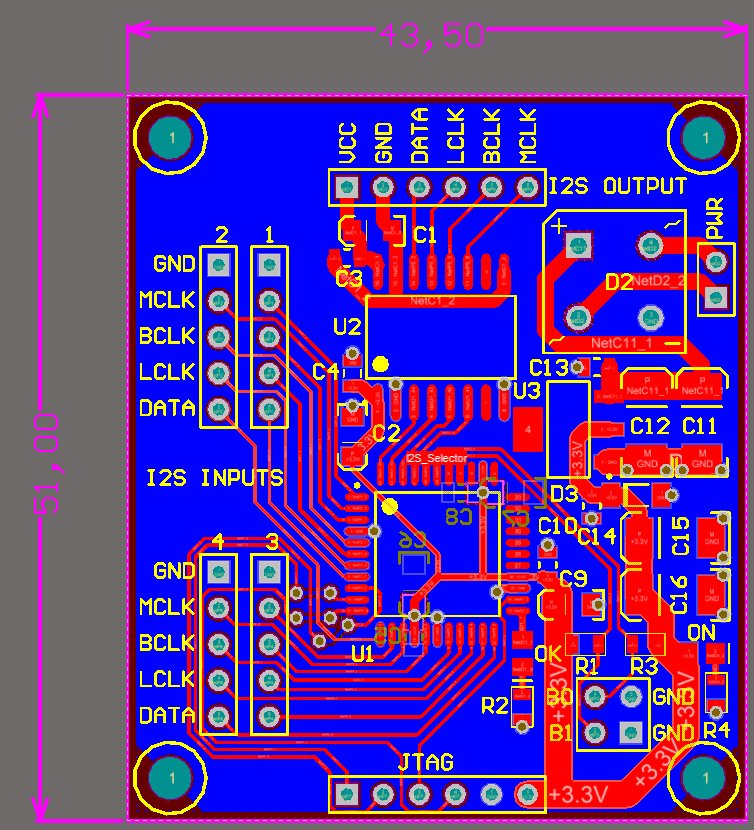

Tragedii raczej nie będzie. Można by przesunąc C2, C3 w lewo, nieco w dól, puścić zasilanie WM8804 dołem, a tą ścieżkę +3.3V dać na top przez zworkę 0805 np. Byłaby masa nieprzerwana nad ścieżką sygnału (RX0). Ewentualnie można zostawić ścieżkę RX0 na top całą. I wtedy z kolei można by puścić +3.3V dołem w miejscu krzyżowania z RX0 przez zworkę SMD. W miejscu krzyżowania pomiędzy +3.3V i RX0 byłaby warstwa masy wtedy.

Aplikacja forum

Jak zainstalować aplikację na iOS

Podążaj za instrukcjami wyświetlonymi na poniższym wideo, aby zainstalować aplikację internetową na Twoim urządzeniu.

Uwaga: Ta opcja może nie być dostępna w niektórych przeglądarkach internetowych.

-

Witamy w największym polskim serwisie internetowym poświęconym w całości zagadnieniom samodzielnej budowy nagłośnienia.

Dzięki DIYaudio.pl poznasz zagadnienia samodzielnej budowy nagłośnienia od podszewki oraz będziesz mógł dyskutować o DIY audio do woli.

Artykuły z dawnego portalu zostały przeniesione do sekcji forum na samym dole.

Twoja przeglądarka jest nieaktualna i może wyświetlać tę stronę nieprawidłowo.

Powinieneś zaktualizować ją lub skorzystać z alternatywnej przeglądarki.

Powinieneś zaktualizować ją lub skorzystać z alternatywnej przeglądarki.

Konwerter USB/SPDIF -> I2S

- Autor wątku scythe1123

- Data rozpoczęcia

Ten temat to dobry przykład jak niby prosta rzecz potrafi sprawić ogromne problemy. Sam się nad tym zastanawiałem, ponieważ czegoś takiego będę potrzebował i wczoraj machnąłem PCB na CPLD XL5792XL:

CPLD za "dychę" a i tak będzie się tam nudził bo w praktyce nic nie ma do robotyMinus to potrzeba programowania układu logiki. Przełączanie wejścia na zwieraniu B0 / B1 do masy układu. Wyjście izolowane na ISO7640 / ADuM1400, więc nie ma problemu z łączeniem masy, ponieważ sygnał wyjściowy jest odseparowany od reszty. Zasilanie jest z transformatora aby się nie męczyć z generowaniem 3,3V dla CPLD.

W każdym wypadku płytki przyjdą to i poskładam, zrobię opis dla CPLD i zobaczymy co z tego wyjdzie.

Na szybkości polutowane i można opisać CPLD

Na szybkości polutowane i można opisać CPLD

Jak uruchomisz, będę Ciebie prosić o schemat - narysuję wtedy PCB "kanapkowe" pod Amanero itp

Hoglin, planujesz, żeby PCB miało kształt Amanero i żeby miało slot na Amanero?

Czemu w zasadzie by tego nie zrobić na wcześniej wspomnianym scalaku ten CPLD to jest overkill.

ten CPLD to jest overkill.

Czemu w zasadzie by tego nie zrobić na wcześniej wspomnianym scalaku

Na 2 wejścia to może i tak, ale na więcej to bym się zastanawiał.ten CPLD to jest overkill.

Masz już coś na oku odnośnie BT->I2S?

Jak uruchomisz, będę Ciebie prosić o schemat - narysuję wtedy PCB "kanapkowe" pod Amanero itp

Jaki schemat? Czy nie chodzi ci czasem o rozmieszczenie gold-pinów?

ten CPLD to jest overkill.

Na 2 wejścia to może i tak, ale na więcej to bym się zastanawiał.

W sumie to tyle w temacie

Chodzi mi o schemat podłączenia CPLD - żebym mógł zrobić bliźniaczą konstrukcję do TwojejJaki schemat? Czy nie chodzi ci czasem o rozmieszczenie gold-pinów?

Coś takiego:Masz już coś na oku odnośnie BT->I2S?

https://www.aliexpress.com/item/CSR...ding-Stereo-Audio-I2S-Output/32827020145.html

Chodzi mi o schemat podłączenia CPLD - żebym mógł zrobić bliźniaczą konstrukcję do Twojej

Piny w CPLD ustawia się podczas programowania, tzw. mapowanie, więc to bez różnicy jaki pin używasz dopóki nie jest potrzeba użycia go jako np. globalnego zegara. Druga sprawa, opisu sprzętu nie wgrasz bez np. Xilinx Platform Cable:

https://allegro.pl/listing?string=x...s-base-relevance-floki-5-nga-hcp-uni-1-2-1003

Niestety nie rozumiem co chcesz osiągnąc

Kod:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity I2S_Selector is

Port (

-- I2S inputs

i2s_data_in : in std_logic_vector(3 downto 0);

i2s_lclk_in : in std_logic_vector(3 downto 0);

i2s_bclk_in : in std_logic_vector(3 downto 0);

i2s_mclk_in : in std_logic_vector(3 downto 0);

-- I2S selection

i2s_sel : in std_logic_vector(1 downto 0);

-- LED

led : out std_logic;

-- I2S output

i2s_data_out : out std_logic;

i2s_lclk_out : out std_logic;

i2s_bclk_out : out std_logic;

i2s_mclk_out : out std_logic);

end I2S_Selector;

architecture Behavioral of I2S_Selector is

begin

led <= '1'; -- indicator

i2s_data_out <= i2s_data_in(conv_integer(i2s_sel));

i2s_lclk_out <= i2s_lclk_in(conv_integer(i2s_sel));

i2s_bclk_out <= i2s_bclk_in(conv_integer(i2s_sel));

i2s_mclk_out <= i2s_mclk_in(conv_integer(i2s_sel));

end Behavioral;

Ostatnia edycja:

jak widziałem dzisiaj co opublikował Holgin to znowu powtórzę  ..marzy mi się taki AK4118 z np 3x optyczne, 3x współosiowe i to by szło na selektor i2s (np ten co pokazał .3lite) ... wyjście i2s każdy podpinał by sobie dowolne...czy to jakis dac z aliexpres... czy soekris...czy AD1865 .3lite

..marzy mi się taki AK4118 z np 3x optyczne, 3x współosiowe i to by szło na selektor i2s (np ten co pokazał .3lite) ... wyjście i2s każdy podpinał by sobie dowolne...czy to jakis dac z aliexpres... czy soekris...czy AD1865 .3lite  . w sumie to nawet selektor na 3 i2s by się przydał bo na aliexpress są fajne moduły BT na I2S więc mozna by było zrobić ze na 1 jest AK4118, na drugim BT a na trzecim albo jakis XMOS albo np raspberry z moode czy volumio ...

. w sumie to nawet selektor na 3 i2s by się przydał bo na aliexpress są fajne moduły BT na I2S więc mozna by było zrobić ze na 1 jest AK4118, na drugim BT a na trzecim albo jakis XMOS albo np raspberry z moode czy volumio ...

- w sumie jedyne sterownie wymagane do tego to przełączanie źródeł w formie: OPT1, OPT2, OPT3, COAX1, COAX2, COAX3, I2S1, I2S2, I2S3 ;p

nie mówcie, że coś takiego nie bylo by piękne ! - każdy ma w domu kilka jakichś źródeł cyfrowych, konsole, tunery satelitarne, TV itp a do tego jest teraz bardzo sporo fajnych DACów z wejsciem I2S...może któryś z doświadczonych projektantów da się namówić ? ;p

chętnie zajął bym się testowaniem itp takiego projektu i dorzucę się do jego powstania

i dorzucę się do jego powstania

- w sumie jedyne sterownie wymagane do tego to przełączanie źródeł w formie: OPT1, OPT2, OPT3, COAX1, COAX2, COAX3, I2S1, I2S2, I2S3 ;p

nie mówcie, że coś takiego nie bylo by piękne ! - każdy ma w domu kilka jakichś źródeł cyfrowych, konsole, tunery satelitarne, TV itp a do tego jest teraz bardzo sporo fajnych DACów z wejsciem I2S...może któryś z doświadczonych projektantów da się namówić ? ;p

chętnie zajął bym się testowaniem itp takiego projektu

Ostatnia edycja:

Piny w CPLD ustawia się podczas programowania, tzw. mapowanie, więc to bez różnicy jaki pin używasz dopóki nie jest potrzeba użycia go jako np. globalnego zegara. Druga sprawa, opisu sprzętu nie wgrasz bez np. Xilinx Platform Cable:

https://allegro.pl/listing?string=x...s-base-relevance-floki-5-nga-hcp-uni-1-2-1003

Niestety nie rozumiem co chcesz osiągnącW każdym wypadku opis samego CPLD do takiego selektora to pierwsze liźnięcie języka opisu sprzętu i nie ma nawet co tu kopiować, ponieważ wygląda to następująco w VHDL:

Kod:library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity I2S_Selector is Port ( -- I2S inputs i2s_data_in : in std_logic_vector(3 downto 0); i2s_lclk_in : in std_logic_vector(3 downto 0); i2s_bclk_in : in std_logic_vector(3 downto 0); i2s_mclk_in : in std_logic_vector(3 downto 0); -- I2S selection i2s_sel : in std_logic_vector(1 downto 0); -- LED led : out std_logic; -- I2S output i2s_data_out : out std_logic; i2s_lclk_out : out std_logic; i2s_bclk_out : out std_logic; i2s_mclk_out : out std_logic); end I2S_Selector; architecture Behavioral of I2S_Selector is begin led <= '1'; -- indicator i2s_data_out <= i2s_data_in(conv_integer(i2s_sel)); i2s_lclk_out <= i2s_lclk_in(conv_integer(i2s_sel)); i2s_bclk_out <= i2s_bclk_in(conv_integer(i2s_sel)); i2s_mclk_out <= i2s_mclk_in(conv_integer(i2s_sel)); end Behavioral;

Chce osiągnąć coś takiego:

Czyli duże PCB, na które wsadza się Amanero oraz dwie sztuki odbiornika na WM8804:

DO tego BT o którym wspomniałem wcześniej, więc mamy 4 źródła I2S i one by szły na CPLD. A o schemat proszę dlatego, bo chciałbym zachować taki sam układ pinów jak Ty, żeby móc w miarę bezmyślnie wgrać ten sam program

Całe rozwiązanie jest dość nieekonomiczne i rozwlekłe, ale akurat w moim przypadku wyjdzie dość tanio, bo 1 odbiornik i PCB już mam, a zamówienie na pcbway i tak będę robić

Selektor już istnieje fizycznie  Pozostaje mi nauka VHDL - to może trochę zająć

Pozostaje mi nauka VHDL - to może trochę zająć

Dodałem LEDy sygnalizujące aktualnie wybrane wyjście, zarówno na PCB, jak i na złączu IDC10, gdyby ktoś chciał sobie wyprowadzić na front Drugie złącze służy za selektor.

Drugie złącze służy za selektor.

Jest Coax, Optical, gniazdo na Amanero/XMOS oraz moduł Bluetooth - już przetestowany, jest całkiem fajny i ma dużą zaletę - złącze na antenę zewnętrzną

Jak układ zadziała, będzie szerzej opisany na forum

Dodałem LEDy sygnalizujące aktualnie wybrane wyjście, zarówno na PCB, jak i na złączu IDC10, gdyby ktoś chciał sobie wyprowadzić na front

Jest Coax, Optical, gniazdo na Amanero/XMOS oraz moduł Bluetooth - już przetestowany, jest całkiem fajny i ma dużą zaletę - złącze na antenę zewnętrzną

Jak układ zadziała, będzie szerzej opisany na forum

Podlinkujesz moduł BT? To od razu sobie zamówię : )

@Holgin

Jakie maksymalne częstotliwości będą obsługiwane na wejściu spdif - zgonie ze specyfikacją 192kHz?

Czy jak użyję amanero to będzie można wykorzystać jego możliwości tzn. 384khz i DSD512?

Trzymam kciuki.

Jakie maksymalne częstotliwości będą obsługiwane na wejściu spdif - zgonie ze specyfikacją 192kHz?

Czy jak użyję amanero to będzie można wykorzystać jego możliwości tzn. 384khz i DSD512?

Trzymam kciuki.

Mój selektor jest gotowy i tutaj go opisałem :@Holgin

Jakie maksymalne częstotliwości będą obsługiwane na wejściu spdif - zgonie ze specyfikacją 192kHz?

Czy jak użyję amanero to będzie można wykorzystać jego możliwości tzn. 384khz i DSD512?

Trzymam kciuki.

https://diyaudio.pl/showthread.php/29450-Selektor-czterech-wejść-cyfrowych-2x-SPDIF-USB-Bluetooth

Tak samo jest wątek o odbiorniku na wm, proszę żebyś tam napisał, żeby pytania, odpowiedzi i inne informacje były w jednym miejscu