Tragedii raczej nie bêdzie. Mo¿na by przesun±c C2, C3 w lewo, nieco w dól, pu¶ciæ zasilanie WM8804 do³em, a t± ¶cie¿kê +3.3V daæ na top przez zworkê 0805 np. By³aby masa nieprzerwana nad ¶cie¿k± sygna³u (RX0). Ewentualnie mo¿na zostawiæ ¶cie¿kê RX0 na top ca³±. I wtedy z kolei mo¿na by pu¶ciæ +3.3V do³em w miejscu krzy¿owania z RX0 przez zworkê SMD. W miejscu krzy¿owania pomiêdzy +3.3V i RX0 by³aby warstwa masy wtedy.

Ogłoszenie

Collapse

No announcement yet.

Konwerter USB/SPDIF -> I2S

Collapse

X

-

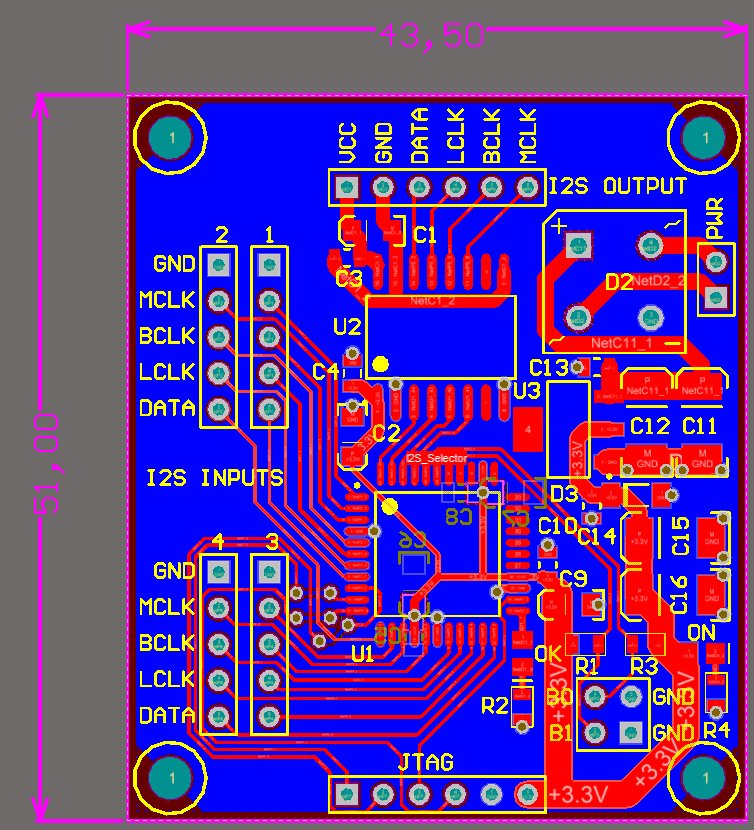

Zamieszczone przez .3lite Zobacz postaTen temat to dobry przyk³ad jak niby prosta rzecz potrafi sprawiæ ogromne problemy. Sam siê nad tym zastanawia³em, poniewa¿ czego¶ takiego bêdê potrzebowa³ i wczoraj machn±³em PCB na CPLD XL5792XL:

CPLD za "dychê" a i tak bêdzie siê tam nudzi³ bo w praktyce nic nie ma do roboty :) Minus to potrzeba programowania uk³adu logiki. Prze³±czanie wej¶cia na zwieraniu B0 / B1 do masy uk³adu. Wyj¶cie izolowane na ISO7640 / ADuM1400, wiêc nie ma problemu z ³±czeniem masy, poniewa¿ sygna³ wyj¶ciowy jest odseparowany od reszty. Zasilanie jest z transformatora aby siê nie mêczyæ z generowaniem 3,3V dla CPLD.

W ka¿dym wypadku p³ytki przyjd± to i posk³adam, zrobiê opis dla CPLD i zobaczymy co z tego wyjdzie.

Na szybko¶ci polutowane i mo¿na opisaæ CPLD :)

Skomentuj

-

Jak uruchomisz, bêdê Ciebie prosiæ o schemat - narysujê wtedy PCB "kanapkowe" pod Amanero itp :)Zamieszczone przez .3lite Zobacz posta

Na szybko¶ci polutowane i mo¿na opisaæ CPLD :)

Skomentuj

-

Na 2 wej¶cia to mo¿e i tak, ale na wiêcej to bym siê zastanawia³. :)Zamieszczone przez scythe1123 Zobacz postaten CPLD to jest overkill.

Skomentuj

-

Jaki schemat? Czy nie chodzi ci czasem o rozmieszczenie gold-pinów?Zamieszczone przez Holgin Zobacz postaJak uruchomisz, bêdê Ciebie prosiæ o schemat - narysujê wtedy PCB "kanapkowe" pod Amanero itp

Zamieszczone przez scythe1123 Zobacz postaten CPLD to jest overkill.W sumie to tyle w temacie :) Ten CPLD w praktyce nic nie robi, ale jak kto¶ ma ochotê to mo¿e siê bawiæ w jakie¶ gotowe multipleksery a potem jako¶ to wszystko prze³±czaæ. Nie do¶æ, ¿e wyjdzie dro¿ej, to jeszcze samo skomplikowanie i wielko¶æ PCB ro¶nie dosyæ znacz±co. Mi siê nie chce bawiæ :)Zamieszczone przez sylvester Zobacz postaNa 2 wej¶cia to mo¿e i tak, ale na wiêcej to bym siê zastanawia³.

Skomentuj

-

Chodzi mi o schemat pod³±czenia CPLD - ¿ebym móg³ zrobiæ bli¼niacz± konstrukcjê do Twojej :)Zamieszczone przez .3lite Zobacz postaJaki schemat? Czy nie chodzi ci czasem o rozmieszczenie gold-pinów?

Co¶ takiego:Zamieszczone przez scythe1123 Zobacz postaMasz ju¿ co¶ na oku odno¶nie BT->I2S?

https://www.aliexpress.com/item/CSRA...827020145.html

Skomentuj

-

Piny w CPLD ustawia siê podczas programowania, tzw. mapowanie, wiêc to bez ró¿nicy jaki pin u¿ywasz dopóki nie jest potrzeba u¿ycia go jako np. globalnego zegara. Druga sprawa, opisu sprzêtu nie wgrasz bez np. Xilinx Platform Cable:Zamieszczone przez Holgin Zobacz postaChodzi mi o schemat pod³±czenia CPLD - ¿ebym móg³ zrobiæ bli¼niacz± konstrukcjê do Twojej

https://allegro.pl/listing?string=xi...p-uni-1-2-1003

Niestety nie rozumiem co chcesz osi±gn±c :) W ka¿dym wypadku opis samego CPLD do takiego selektora to pierwsze li¼niêcie jêzyka opisu sprzêtu i nie ma nawet co tu kopiowaæ, poniewa¿ wygl±da to nastêpuj±co w VHDL:

[code]library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity I2S_Selector is

Port (

-- I2S inputs

i2s_data_in : in std_logic_vector(3 downto 0);

i2s_lclk_in : in std_logic_vector(3 downto 0);

i2s_bclk_in : in std_logic_vector(3 downto 0);

i2s_mclk_in : in std_logic_vector(3 downto 0);

-- I2S selection

i2s_sel : in std_logic_vector(1 downto 0);

-- LED

led : out std_logic;

-- I2S output

i2s_data_out : out std_logic;

i2s_lclk_out : out std_logic;

i2s_bclk_out : out std_logic;

i2s_mclk_out : out std_logic);

end I2S_Selector;

architecture Behavioral of I2S_Selector is

begin

led <= '1'; -- indicator

i2s_data_out <= i2s_data_in(conv_integer(i2s_sel));

i2s_lclk_out <= i2s_lclk_in(conv_integer(i2s_sel));

i2s_bclk_out <= i2s_bclk_in(conv_integer(i2s_sel));

i2s_mclk_out <= i2s_mclk_in(conv_integer(i2s_sel));

end Behavioral;

[/code]Last edited by .3lite; 09.03.2018, 17:49.

Skomentuj

-

jak widzia³em dzisiaj co opublikowa³ Holgin to znowu powtórzê ..marzy mi siê taki AK4118 z np 3x optyczne, 3x wspó³osiowe i to by sz³o na selektor i2s (np ten co pokaza³ .3lite) ... wyj¶cie i2s ka¿dy podpina³ by sobie dowolne...czy to jakis dac z aliexpres... czy soekris...czy AD1865 .3lite :). w sumie to nawet selektor na 3 i2s by siê przyda³ bo na aliexpress s± fajne modu³y BT na I2S wiêc mozna by by³o zrobiæ ze na 1 jest AK4118, na drugim BT a na trzecim albo jakis XMOS albo np raspberry z moode czy volumio ...

..marzy mi siê taki AK4118 z np 3x optyczne, 3x wspó³osiowe i to by sz³o na selektor i2s (np ten co pokaza³ .3lite) ... wyj¶cie i2s ka¿dy podpina³ by sobie dowolne...czy to jakis dac z aliexpres... czy soekris...czy AD1865 .3lite :). w sumie to nawet selektor na 3 i2s by siê przyda³ bo na aliexpress s± fajne modu³y BT na I2S wiêc mozna by by³o zrobiæ ze na 1 jest AK4118, na drugim BT a na trzecim albo jakis XMOS albo np raspberry z moode czy volumio ...

- w sumie jedyne sterownie wymagane do tego to prze³±czanie ¼róde³ w formie: OPT1, OPT2, OPT3, COAX1, COAX2, COAX3, I2S1, I2S2, I2S3 ;p

nie mówcie, ¿e co¶ takiego nie bylo by piêkne ! - ka¿dy ma w domu kilka jakich¶ ¼róde³ cyfrowych, konsole, tunery satelitarne, TV itp a do tego jest teraz bardzo sporo fajnych DACów z wejsciem I2S...mo¿e który¶ z do¶wiadczonych projektantów da siê namówiæ ? ;p

chêtnie zaj±³ bym siê testowaniem itp takiego projektu i dorzucê siê do jego powstania

Last edited by bawolek; 10.03.2018, 19:42.

i dorzucê siê do jego powstania

Last edited by bawolek; 10.03.2018, 19:42.

Skomentuj

-

Chce osi±gn±æ co¶ takiego:Zamieszczone przez .3lite Zobacz postaPiny w CPLD ustawia siê podczas programowania, tzw. mapowanie, wiêc to bez ró¿nicy jaki pin u¿ywasz dopóki nie jest potrzeba u¿ycia go jako np. globalnego zegara. Druga sprawa, opisu sprzêtu nie wgrasz bez np. Xilinx Platform Cable:

https://allegro.pl/listing?string=xi...p-uni-1-2-1003

Niestety nie rozumiem co chcesz osi±gn±c :) W ka¿dym wypadku opis samego CPLD do takiego selektora to pierwsze li¼niêcie jêzyka opisu sprzêtu i nie ma nawet co tu kopiowaæ, poniewa¿ wygl±da to nastêpuj±co w VHDL:

[code]library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity I2S_Selector is

Port (

-- I2S inputs

i2s_data_in : in std_logic_vector(3 downto 0);

i2s_lclk_in : in std_logic_vector(3 downto 0);

i2s_bclk_in : in std_logic_vector(3 downto 0);

i2s_mclk_in : in std_logic_vector(3 downto 0);

-- I2S selection

i2s_sel : in std_logic_vector(1 downto 0);

-- LED

led : out std_logic;

-- I2S output

i2s_data_out : out std_logic;

i2s_lclk_out : out std_logic;

i2s_bclk_out : out std_logic;

i2s_mclk_out : out std_logic);

end I2S_Selector;

architecture Behavioral of I2S_Selector is

begin

led <= '1'; -- indicator

i2s_data_out <= i2s_data_in(conv_integer(i2s_sel));

i2s_lclk_out <= i2s_lclk_in(conv_integer(i2s_sel));

i2s_bclk_out <= i2s_bclk_in(conv_integer(i2s_sel));

i2s_mclk_out <= i2s_mclk_in(conv_integer(i2s_sel));

end Behavioral;

[/code]

Czyli du¿e PCB, na które wsadza siê Amanero oraz dwie sztuki odbiornika na WM8804:

DO tego BT o którym wspomnia³em wcze¶niej, wiêc mamy 4 ¼ród³a I2S i one by sz³y na CPLD. A o schemat proszê dlatego, bo chcia³bym zachowaæ taki sam uk³ad pinów jak Ty, ¿eby móc w miarê bezmy¶lnie wgraæ ten sam program :P Programator uda mi siê po¿yczyæ w pracy/na uczelni w razie czego.

Ca³e rozwi±zanie jest do¶æ nieekonomiczne i rozwlek³e, ale akurat w moim przypadku wyjdzie do¶æ tanio, bo 1 odbiornik i PCB ju¿ mam, a zamówienie na pcbway i tak bêdê robiæ :)

Skomentuj

-

Selektor ju¿ istnieje fizycznie :) Pozostaje mi nauka VHDL - to mo¿e trochê zaj±æ :P

Doda³em LEDy sygnalizuj±ce aktualnie wybrane wyj¶cie, zarówno na PCB, jak i na z³±czu IDC10, gdyby kto¶ chcia³ sobie wyprowadziæ na front :) Drugie z³±cze s³u¿y za selektor.

Jest Coax, Optical, gniazdo na Amanero/XMOS oraz modu³ Bluetooth - ju¿ przetestowany, jest ca³kiem fajny i ma du¿± zaletê - z³±cze na antenê zewnêtrzn± :)

Jak uk³ad zadzia³a, bêdzie szerzej opisany na forum :)

Skomentuj

-

Mój selektor jest gotowy i tutaj go opisa³em :Zamieszczone przez misiaczekmarek Zobacz posta@Holgin

Jakie maksymalne czêstotliwo¶ci bêd± obs³ugiwane na wej¶ciu spdif - zgonie ze specyfikacj± 192kHz?

Czy jak u¿yjê amanero to bêdzie mo¿na wykorzystaæ jego mo¿liwo¶ci tzn. 384khz i DSD512?

Trzymam kciuki.

https://diyaudio.pl/showthread.php/2...-USB-Bluetooth

Tak samo jest w±tek o odbiorniku na wm, proszê ¿eby¶ tam napisa³, ¿eby pytania, odpowiedzi i inne informacje by³y w jednym miejscu :)

Skomentuj

Skomentuj