W rs-online możesz kupić ile dusza zapragnie

No widzisz, nie sądziłem, że mają na stanie do szybkiej realizacji

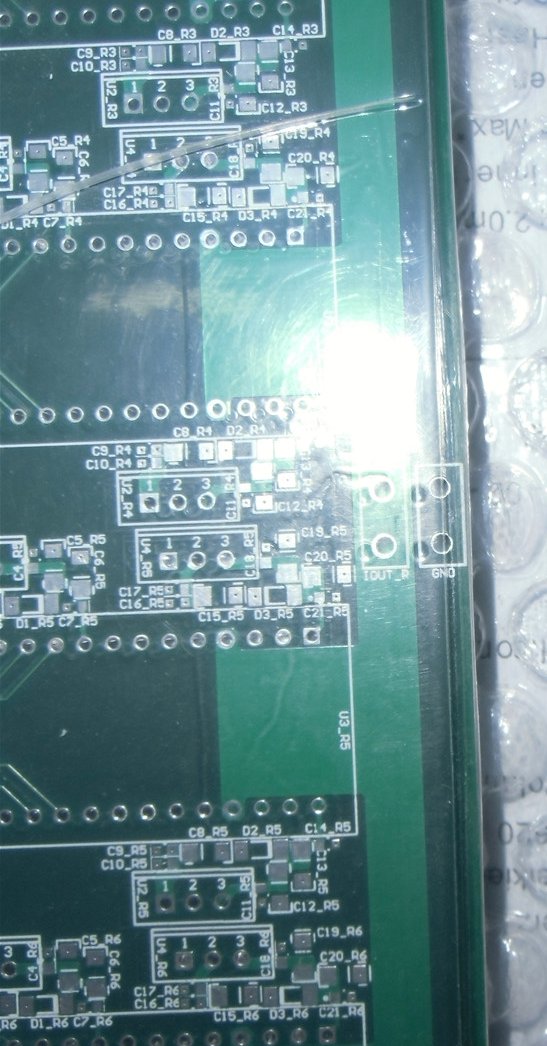

Płytka czterowarstwowa ?

Tak, projekt płytki jest na czterech warstwach.

Podążaj za instrukcjami wyświetlonymi na poniższym wideo, aby zainstalować aplikację internetową na Twoim urządzeniu.

Uwaga: Ta opcja może nie być dostępna w niektórych przeglądarkach internetowych.

W rs-online możesz kupić ile dusza zapragnie

Płytka czterowarstwowa ?

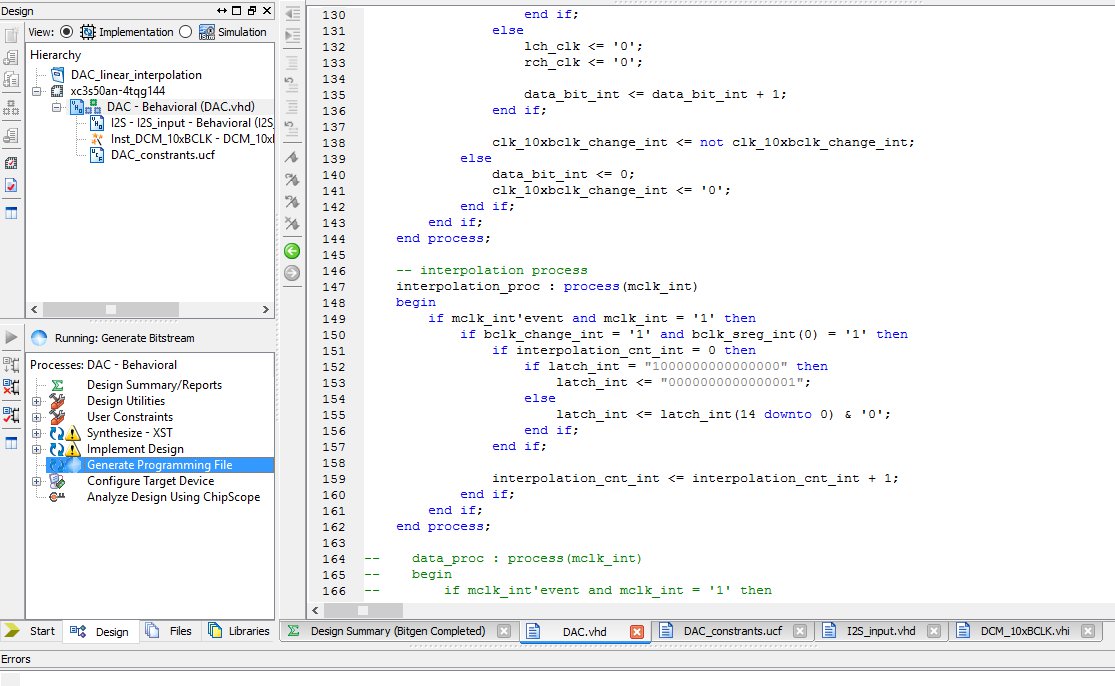

W verilogu pewnie kodu bylo by duzo mniejCały opis sprzętu będzie zrobiony w VHDL'u, ponieważ niestety nie jestem fanem Veriloga

W verilogu pewnie kodu bylo by duzo mniej

Xilinx wybrany przez bardziej przyjazne srodowisko czy akurat ma cos czego alterze brakuje ?

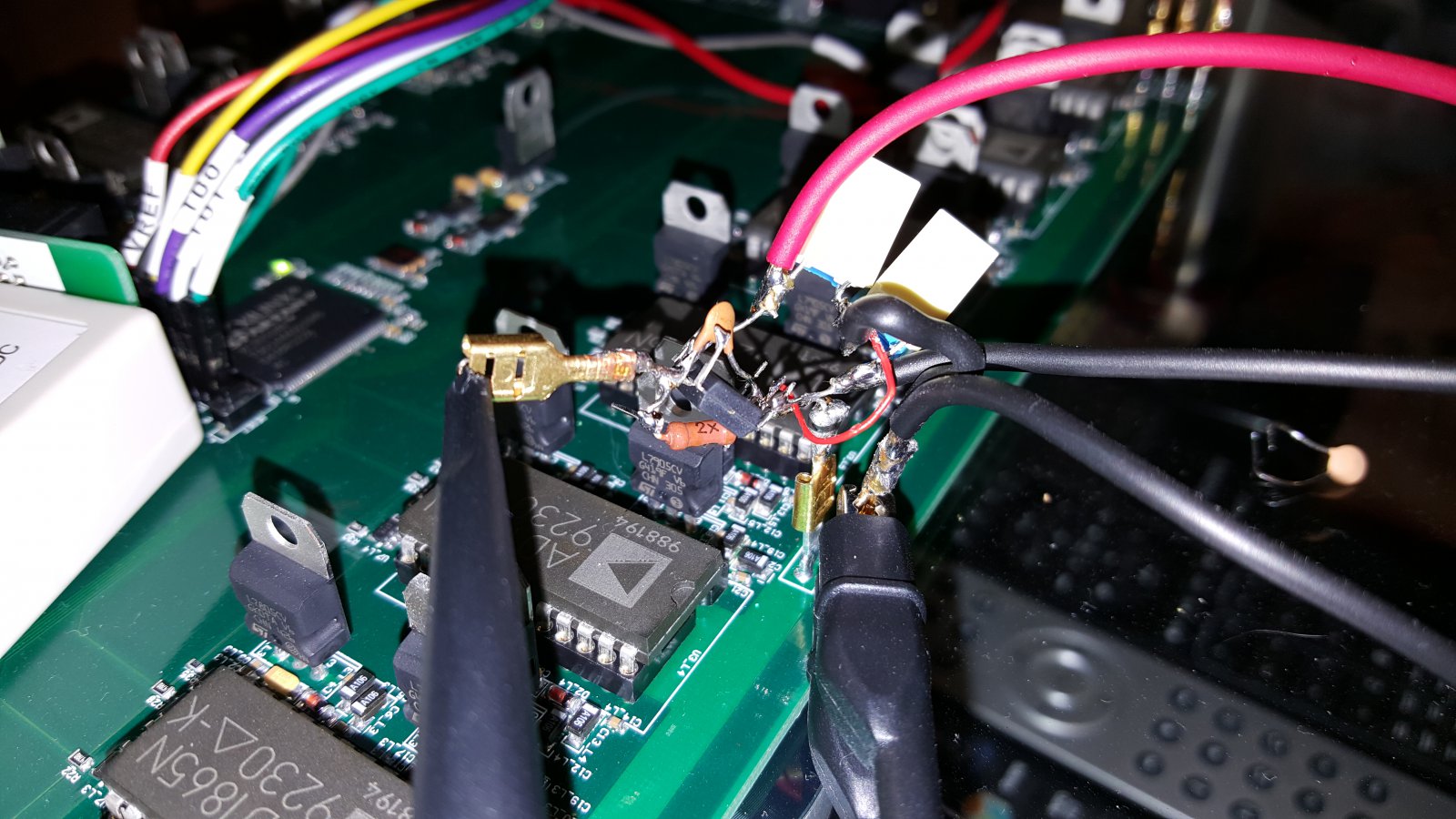

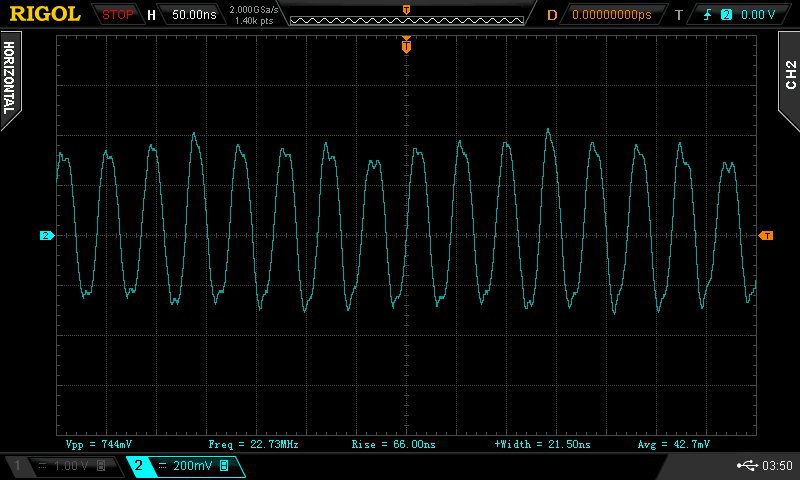

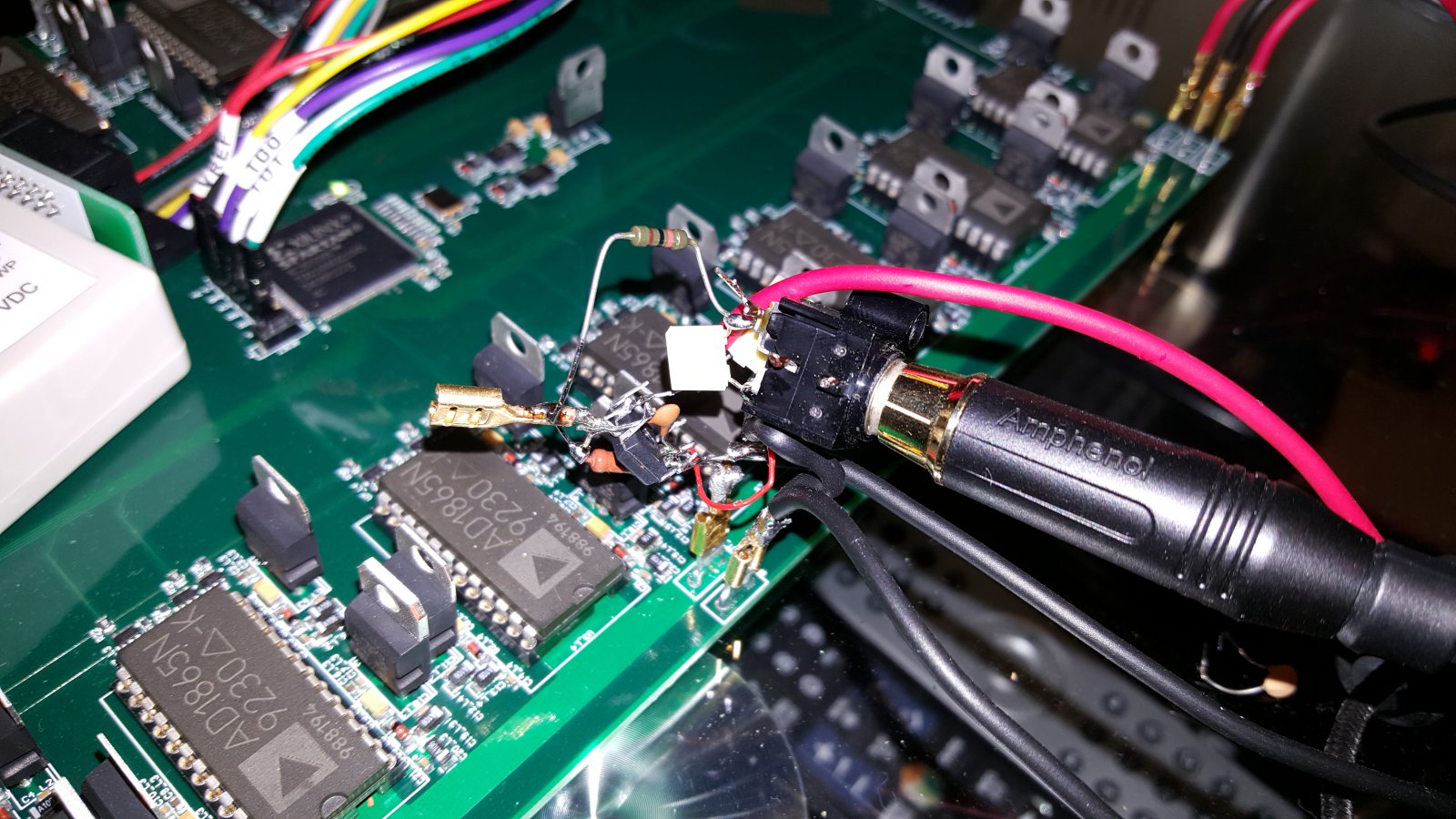

I łykać spory prądi z małą impedancją wejściową przy takich częstotliwościach.

Kiedyś na nich coś tam robiłem .Altery

I łykać spory prąd

Z tą licą to bym nie przesadzał na pewno połączenie powinno być możliwie krótkie .

Szybko działasz

Kiedyś na nich coś tam robiłem .

Ogólnie jak piszesz w HDL to nie ma różnicy wielkiej .

Było to parę lat temu i wtedy bardziej podobało mi się ich IDE było szybsze ten darmowy WebPack od Xilinx się ślimaczy .

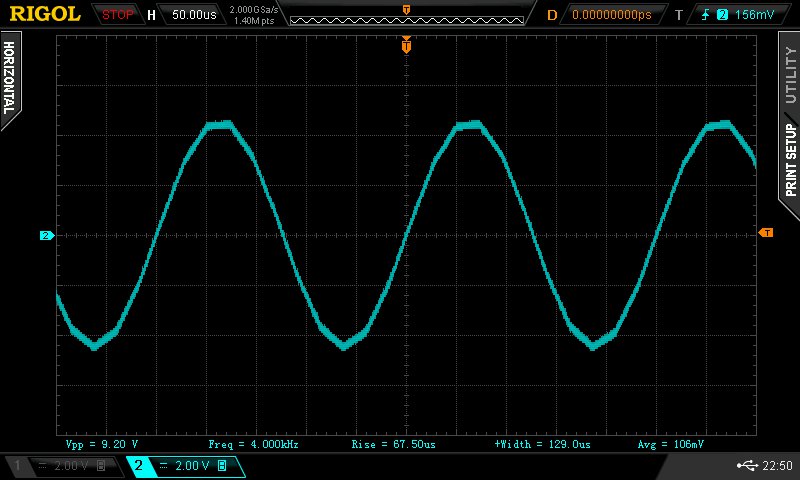

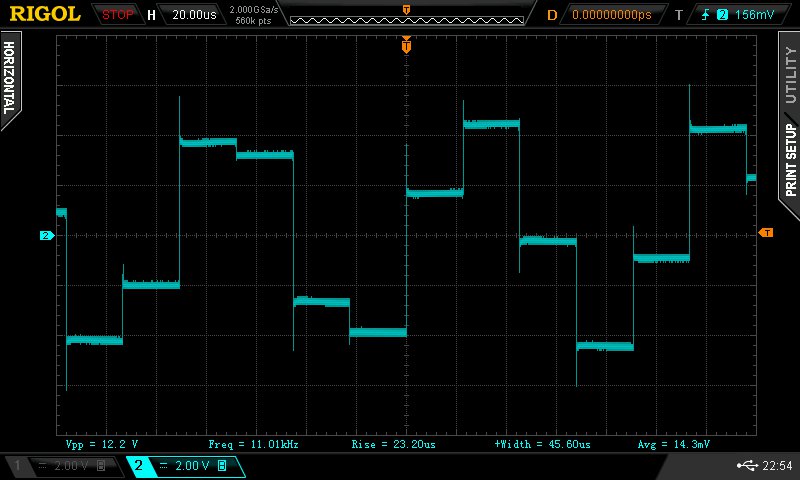

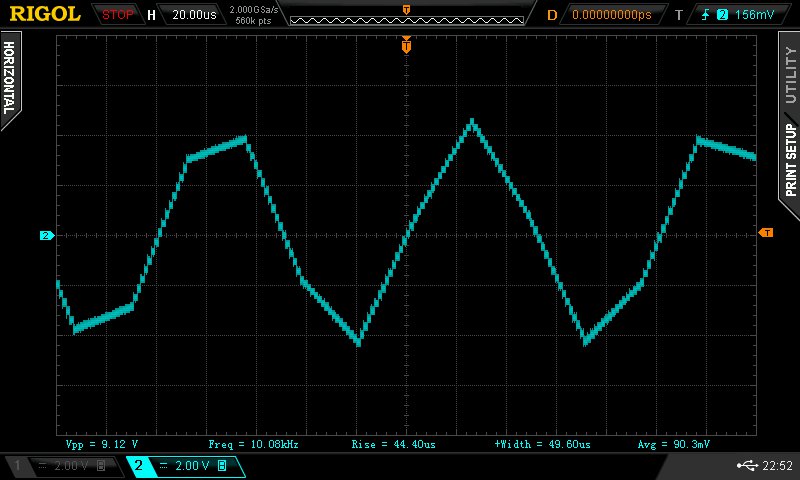

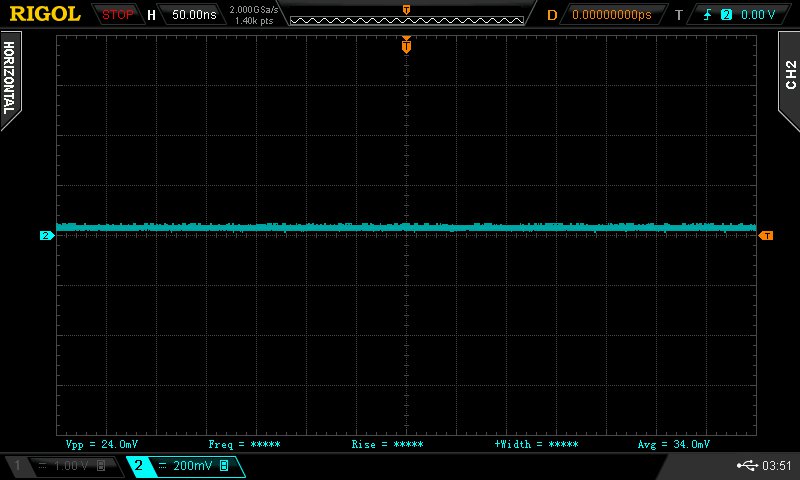

Mam amatorsike pytanie, może się pochylisz, czemu ten sinus 10k taki połamany? Tak wygląda 44,1k?

Może mniejsza wartość by była OK np 30om tylko trzeba by potem wzmocnić sygnał do standardowych 2V .Niestety z doświadczenia dowiedziałem się, że prosty I/V na rezystorze to czysty idiotyzm - DAC'i

http://www.waltjung.org/PDFs/High_Performance_Audio_Stages_Using_TransZ_Amps.pdf

"Murphy gets me ever single time"Popełniłem też pewien błąd myślowy przy projektowaniu układu.

Bo nie ma żadnego filtrowania i występuje aliasing .Mam amatorsike pytanie, może się pochylisz, czemu ten sinus 10k taki połamany? Tak wygląda 44,1k?

Może mniejsza wartość by była OK np 30om tylko trzeba by potem wzmocnić sygnał do standardowych 2V .

Przy 16mA mogło by to działać

http://www.waltjung.org/PDFs/High_Pe...ransZ_Amps.pdf

i strona 124

http://www.analog.com/library/analog...h1_final_R.pdf

"Murphy gets me ever single time"

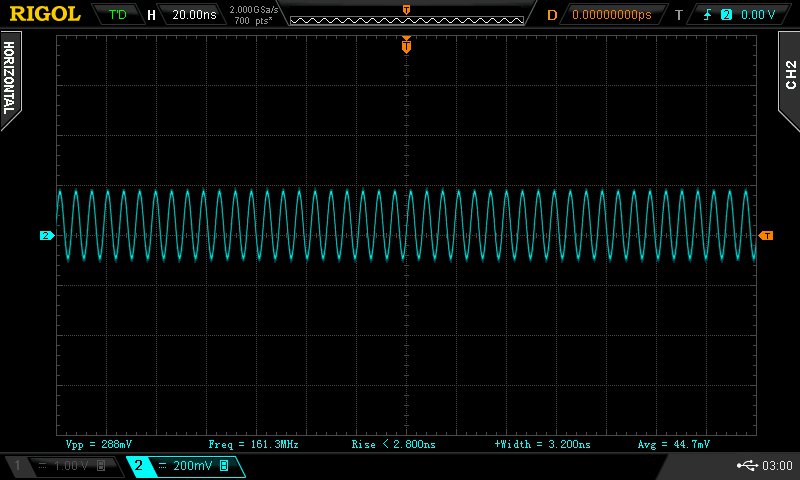

common-mode zapewne .

daj izolator

Albo rozplanowac jakos inaczej powroty pradu zegara. Najlepsza opcja to chyba izolacja.